## RICE UNIVERSITY

## Design of Prototyping Platforms for Multiple Antenna Wireless Communications

by

Patrick O. Murphy

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

#### MASTER OF SCIENCE

APPROVED, THESIS COMMITTEE:

Behnaam Aazhang, Chair J.S. Abercrombie Professor of Electrical and Computer Engineering

Edward W. Knightly Associate Professor of Electrical and Computer Engineering and Computer Science

Ashutosh Sabharwal Faculty Fellow in Electrical and Computer Engineering

Houston, Texas April 2005

#### **ABSTRACT**

# Design of Prototyping Platforms for Multiple Antenna Wireless Communications

by

### Patrick O. Murphy

As the demand for higher performance wireless communications continues to grow, novel algorithms have been developed which provide increased performance and efficiency. One such class of algorithms involves the use of multiple antennas on either end of a wireless link. Many of these multiple input multiple output (MIMO) algorithms offer impressive performance gains over their single antenna counterparts. The practicality of implementing such algorithms in a real system, however, has received far less attention. A primary reason for this is the scarcity of hardware platforms suitable for implementing and evaluating complex wireless communications algorithms. We present in this thesis two such platforms designed specifically to fill this void. The first platform is constructed from commercial off the shelf hardware, including equipment for baseband processing, RF up/downconversion and wireless channel emulation. The second, more ambitious platform, is built from custom hardware designed specifically for flexible MIMO prototyping.

# Acknowledgments

I would like to thank my mentors, colleagues, family and friends for their undending support and encouragement. I would also like to thank our friends in industry, especially at Xilinx and Maxim. Their design advice and generous component donations made this work possible.

# Contents

|   | Abs                          | tract                            |                                                | 11 |

|---|------------------------------|----------------------------------|------------------------------------------------|----|

|   | Acknowledgments              |                                  |                                                |    |

|   | List                         | List of Figures                  |                                                |    |

|   | List of Tables               |                                  |                                                | ix |

| 1 | Introduction                 |                                  |                                                | 1  |

| 2 | 2 Off-the-shelf MIMO Testbed |                                  |                                                | 4  |

|   | 2.1                          | Introd                           | luction                                        | 4  |

|   | 2.2 Testbed Design           |                                  |                                                | 4  |

|   |                              | 2.2.1                            | Baseband Hardware                              | 4  |

|   |                              | 2.2.2                            | RF Hardware                                    | 6  |

|   |                              | 2.2.3                            | Wireless Channel Emulation                     | 7  |

|   | 2.3                          | Applie                           | cation Example: Alamouti Space Time Block Code | 9  |

|   |                              | 2.3.1                            | Implementation Challenges                      | 10 |

|   |                              | 2.3.2                            | Implementation Results                         | 12 |

|   |                              | 2.3.3                            | Verification                                   | 22 |

| 3 | Tra                          | $\operatorname{nsit} \mathbf{A}$ | ccess Point Platform                           | 24 |

|   | 3.1                          | Introd                           | luction                                        | 24 |

|              | 3.2 | Platfo | rm Requirements                     | 25 |

|--------------|-----|--------|-------------------------------------|----|

|              |     | 3.2.1  | Wireless Interfaces                 | 26 |

|              |     | 3.2.2  | Processing Resources                | 27 |

|              |     | 3.2.3  | Flexibility                         | 27 |

|              | 3.3 | High-l | evel Design Decisions               | 28 |

|              |     | 3.3.1  | Custom Hardware                     | 28 |

|              |     | 3.3.2  | Core Components                     | 28 |

|              |     | 3.3.3  | Hardware Partitioning               | 30 |

|              | 3.4 | Hardw  | vare Design                         | 32 |

|              |     | 3.4.1  | Wireless Interface Board            | 33 |

|              |     | 3.4.2  | Radio Board                         | 42 |

|              |     | 3.4.3  | Wired Network Board                 | 47 |

|              | 3.5 | Applic | eations                             | 48 |

|              |     | 3.5.1  | Multi-hop Fixed Wireless Networks   | 48 |

|              |     | 3.5.2  | Real-time Networking Experiments    | 50 |

| 4            | Con | clusio | ns and Future Work                  | 53 |

| $\mathbf{A}$ | PCI | B Sche | ematics                             | 55 |

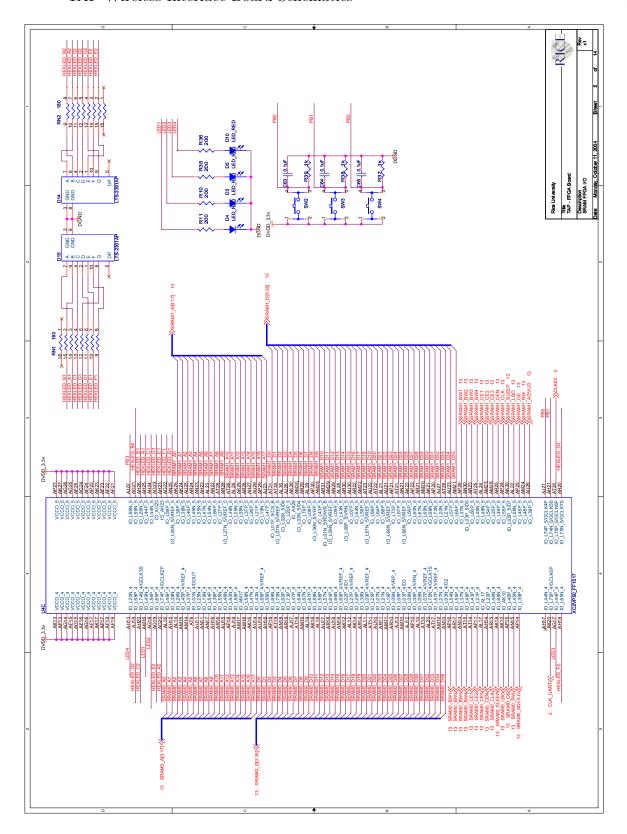

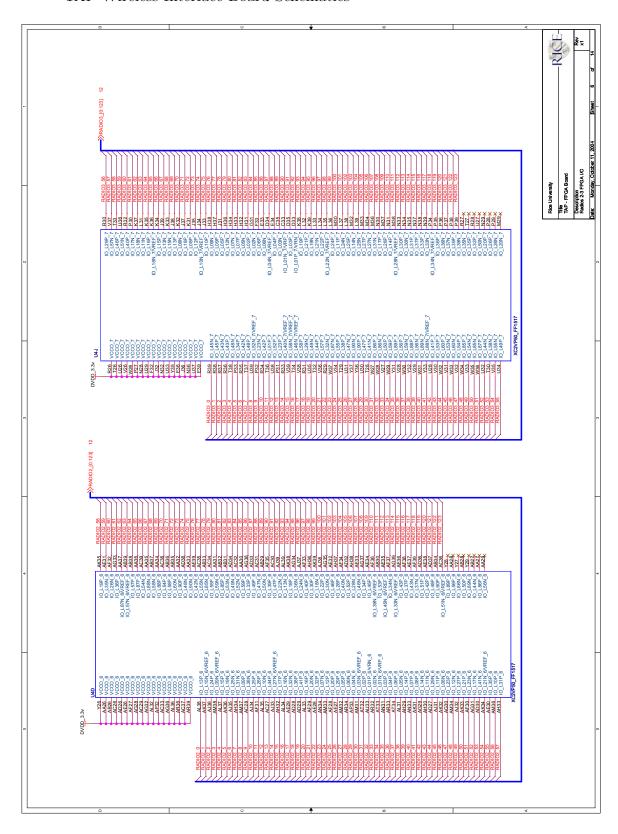

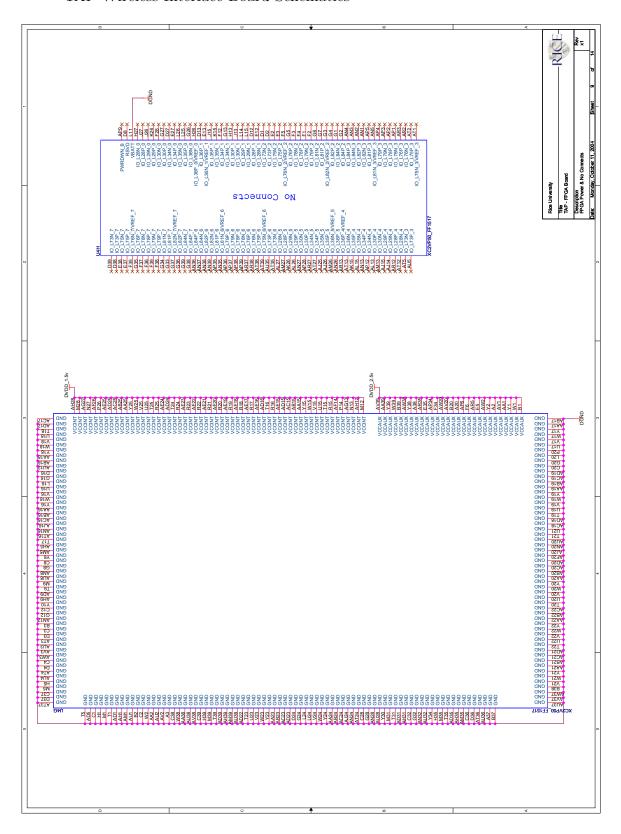

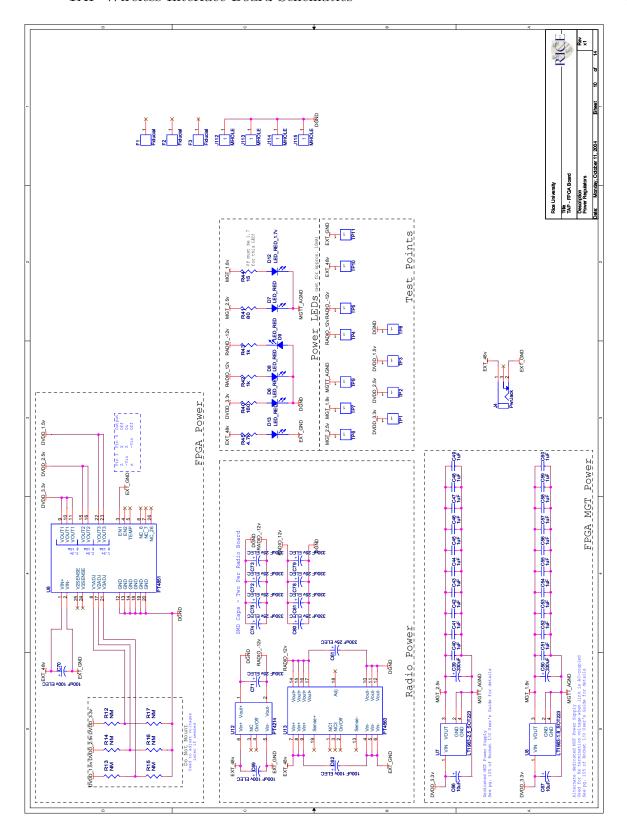

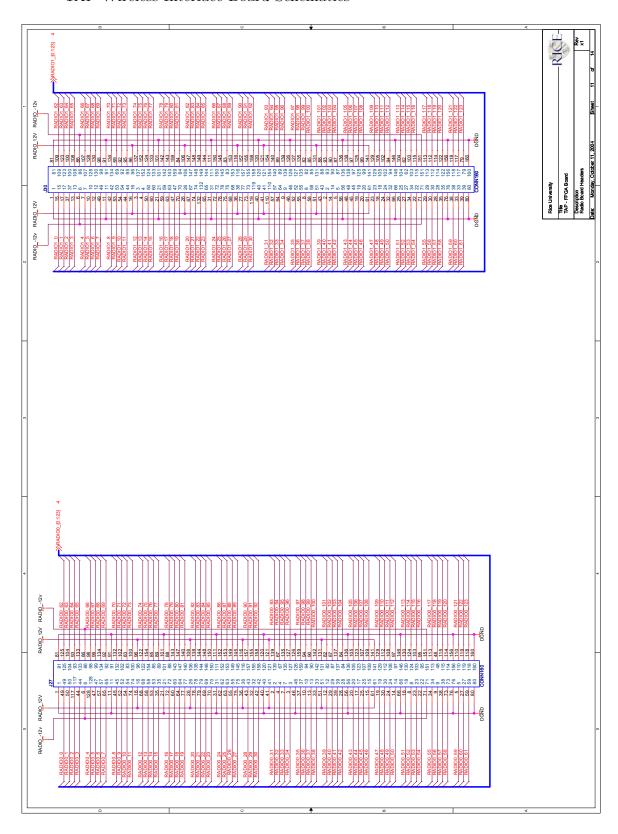

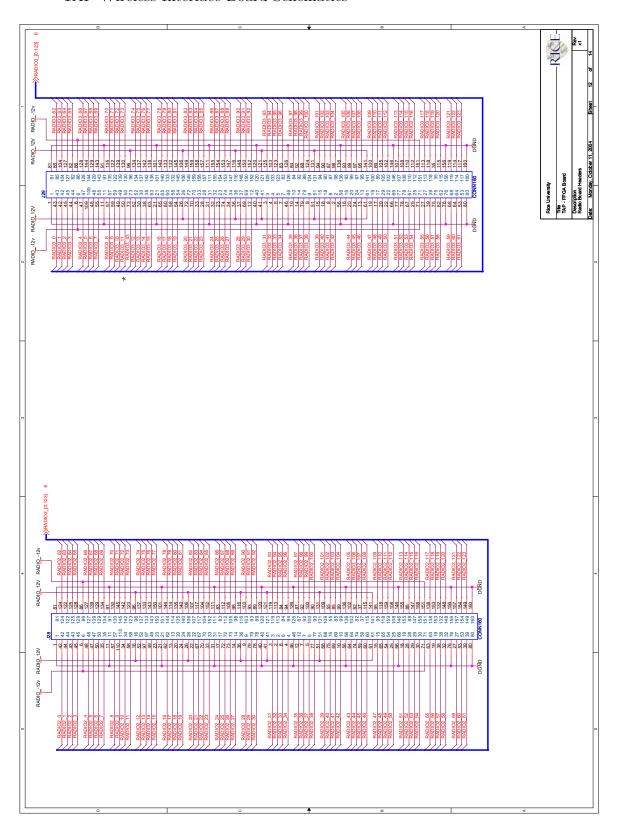

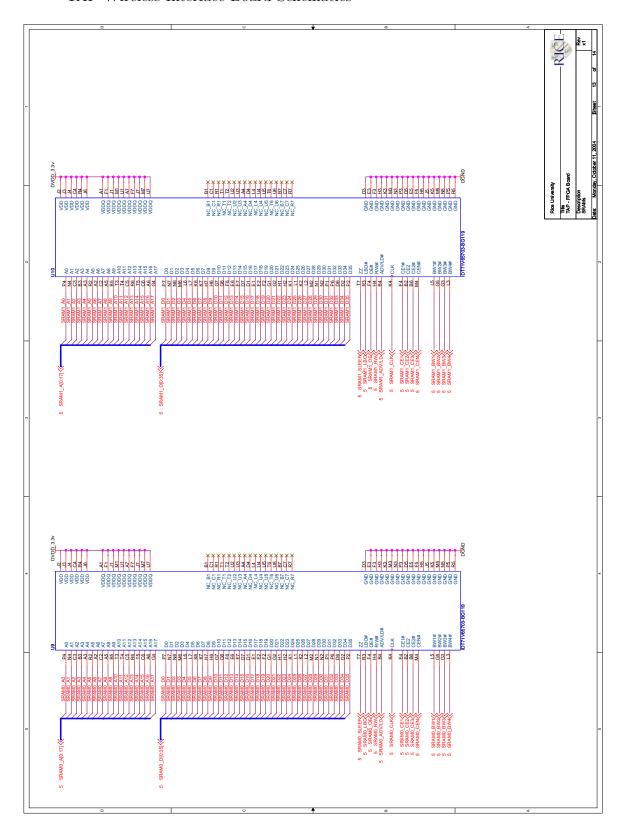

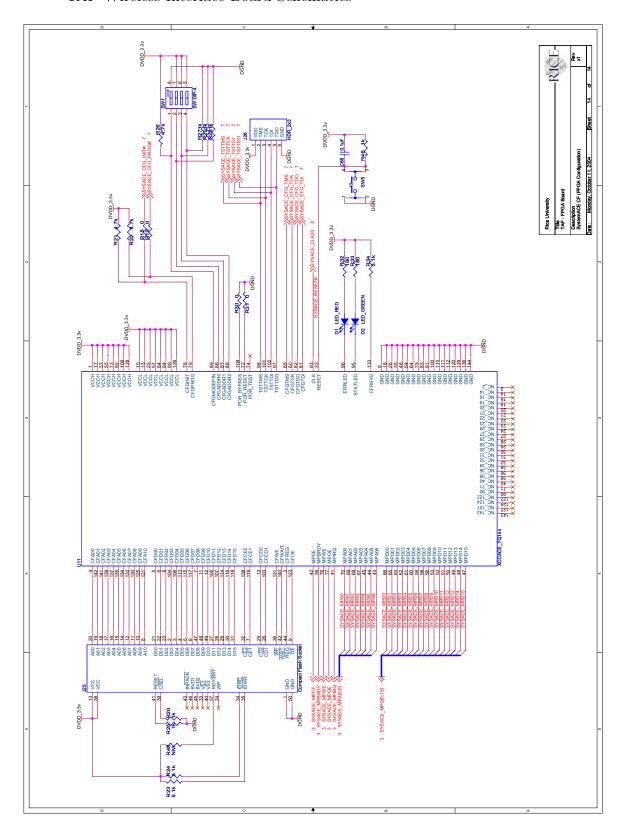

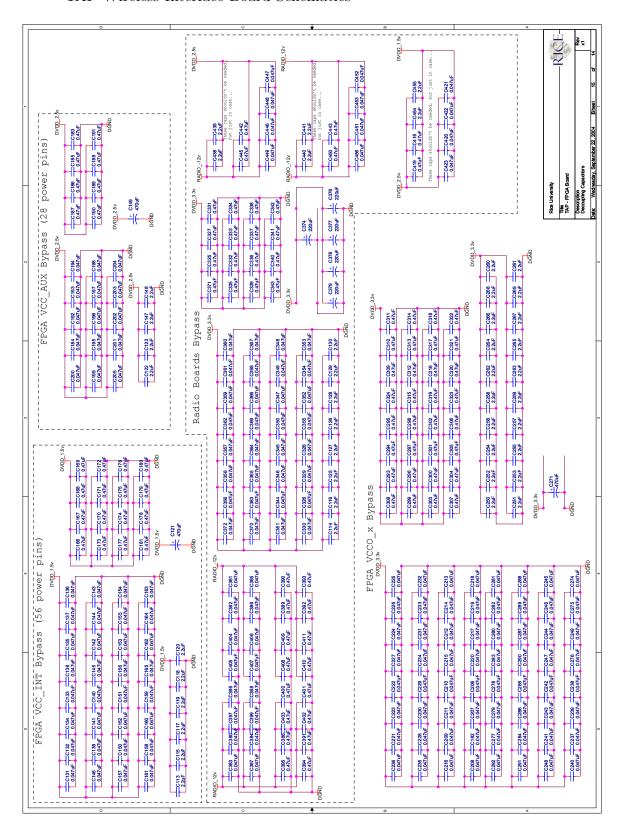

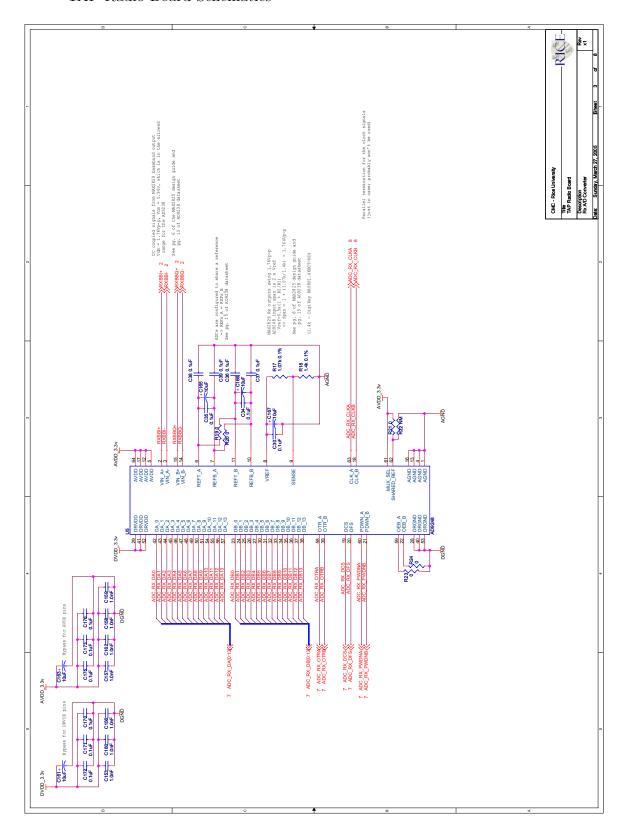

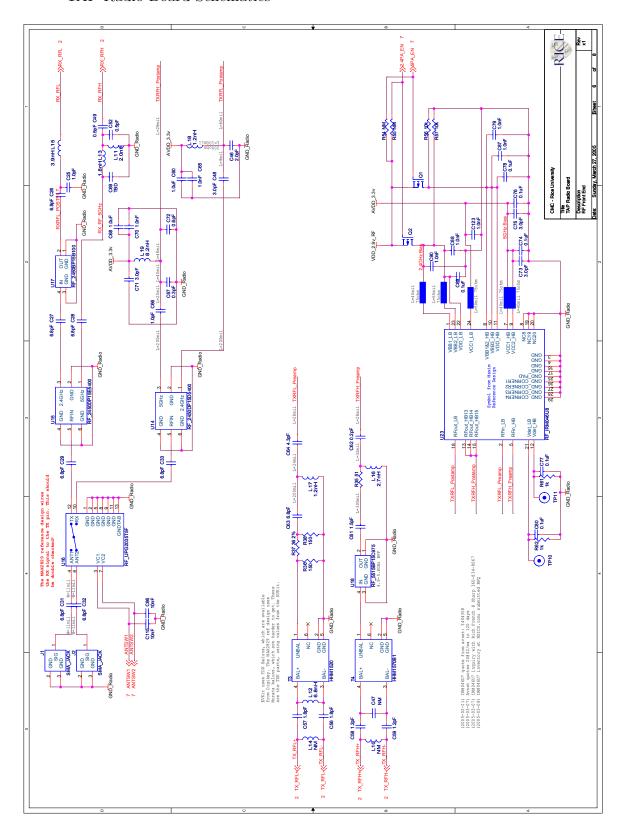

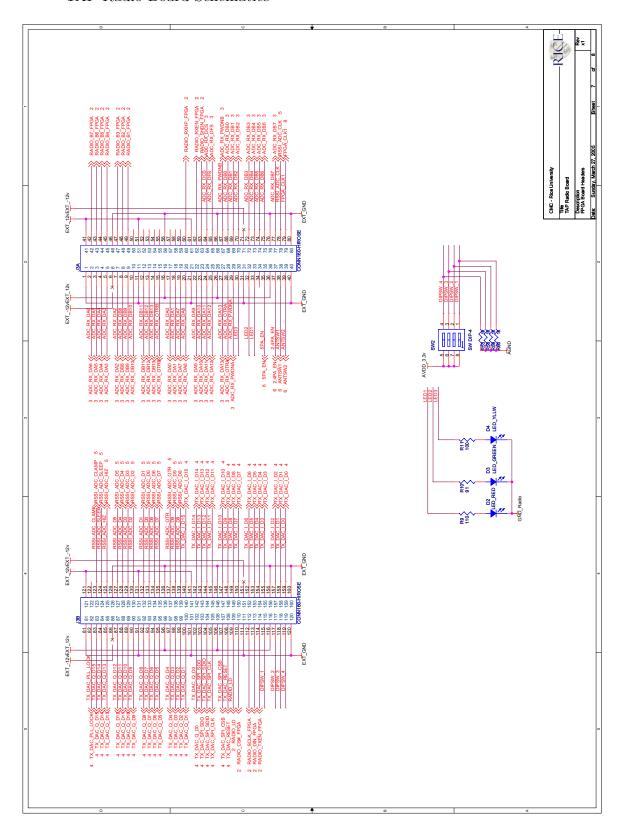

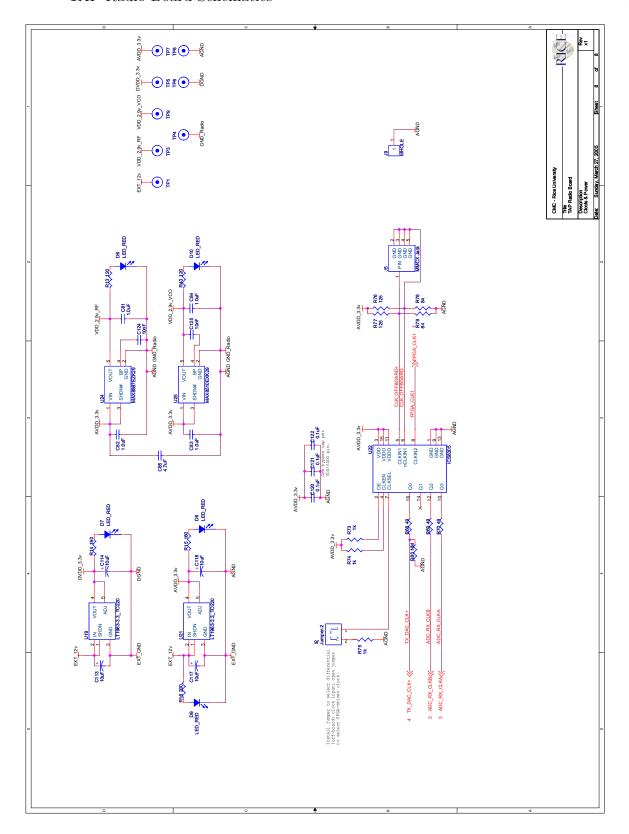

|              | A.1 | TAP V  | Wireless Interface Board Schematics | 55 |

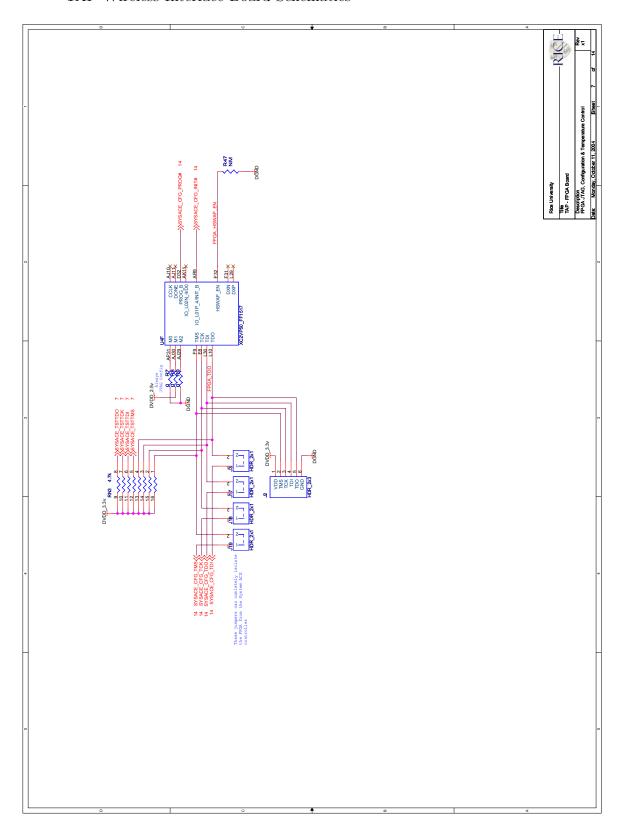

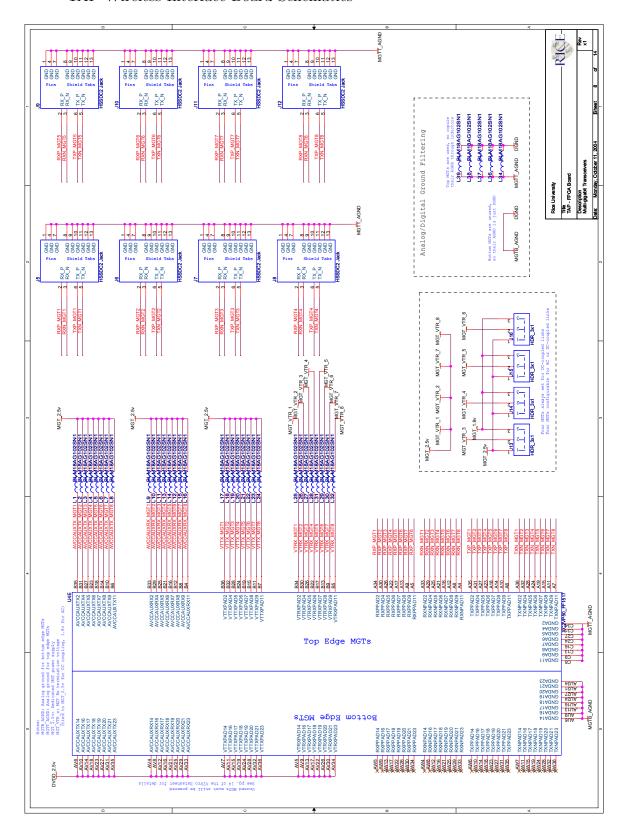

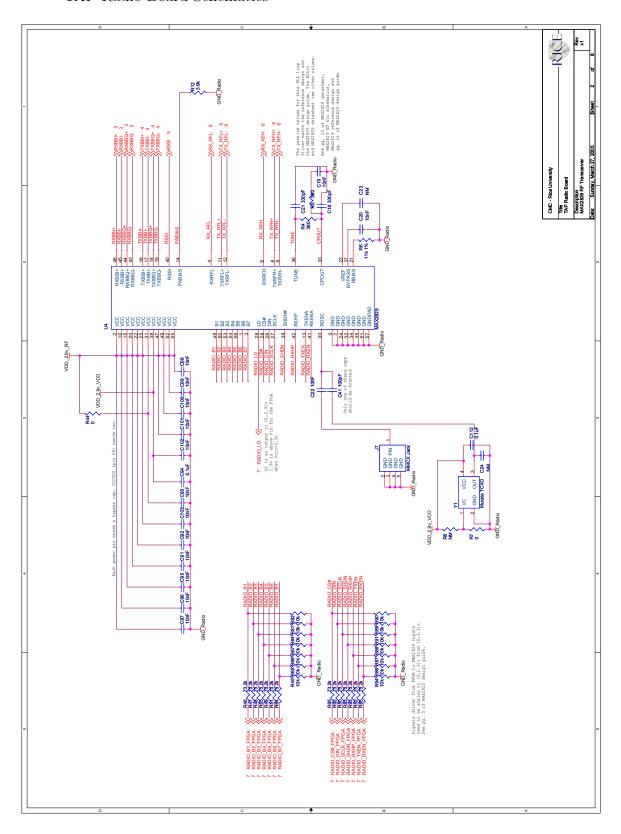

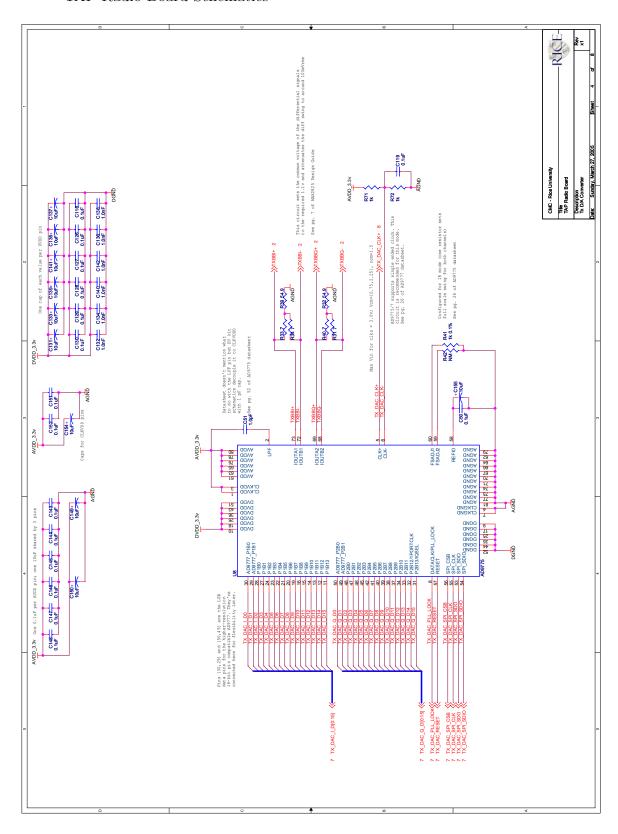

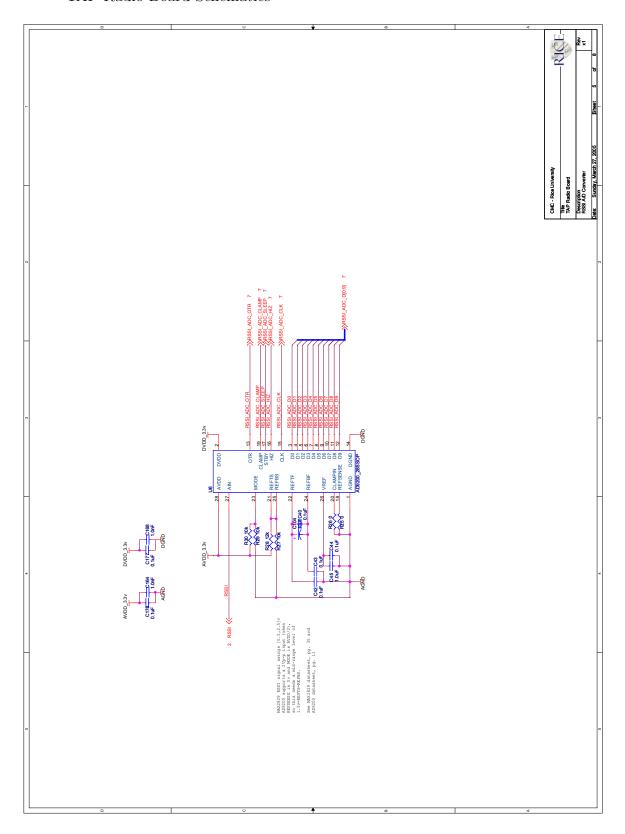

|              | A.2 | TAP I  | Radio Board Schematics              | 71 |

|   |      |                                        | vi   |  |

|---|------|----------------------------------------|------|--|

| В | TAF  | P Wireless Interface Board Users Guide | 80   |  |

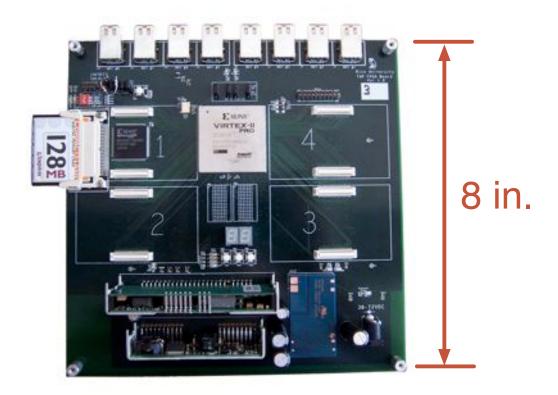

|   | B.1  | Board Overview                         | . 80 |  |

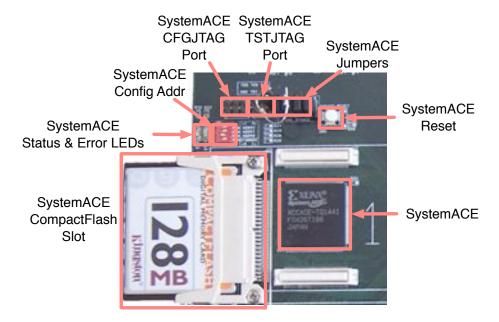

|   |      | B.1.1 SystemACE and FPGA Configuration | . 80 |  |

|   |      | B.1.2 Power                            | . 82 |  |

|   |      | B.1.3 MGTs and Digital I/O             | . 84 |  |

|   |      | B.1.4 User I/O                         | . 85 |  |

|   |      | B.1.5 Daughtercard Slots               | . 87 |  |

|   | B.2  | SRAM                                   | . 89 |  |

|   | В.3  | FPGA Pin Mappings                      | . 90 |  |

|   | Refe | erences                                | 98   |  |

# List of Figures

| 2.1 | FPGA-based processing board                      | 6  |

|-----|--------------------------------------------------|----|

| 2.2 | Emulated wireless channel                        | 8  |

| 2.3 | Testbed connectivity for half-duplex testing     | 8  |

| 2.4 | System Generator model of Alamouti transmitter   | 13 |

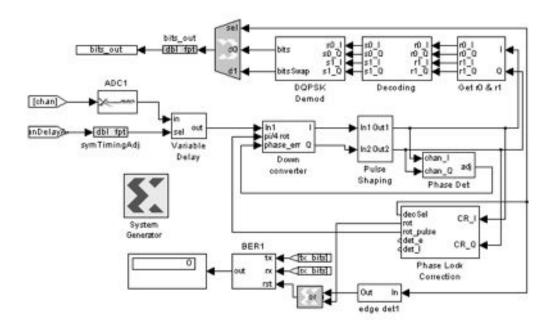

| 2.5 | System Generator model of Alamouti receiver      | 14 |

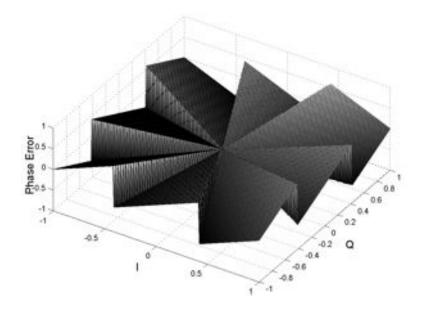

| 2.6 | Carrier recovery phase error estimation function | 18 |

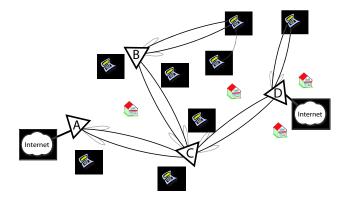

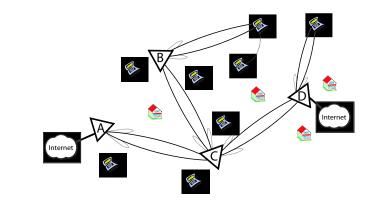

| 3.1 | Example transit access point network             | 25 |

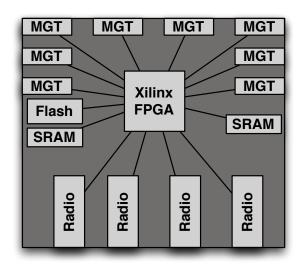

| 3.2 | TAP wireless interface board                     | 33 |

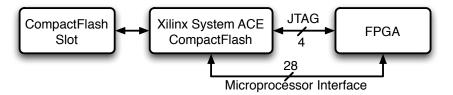

| 3.3 | TAP FPGA configuration system                    | 37 |

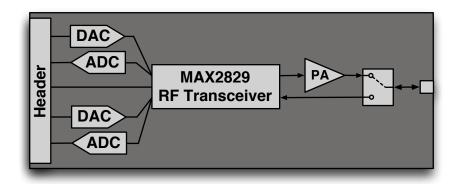

| 3.4 | TAP radio board                                  | 42 |

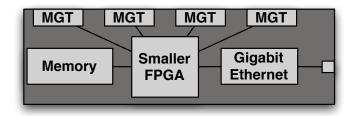

| 3.5 | TAP wired network board                          | 48 |

| 3.6 | TAP network                                      | 49 |

| 3.7 | Building TAPs                                    | 49 |

| В.1 | TAP wireless interface board photo               | 81 |

| B.2 | SystemACE and FPGA configuration                 | 82 |

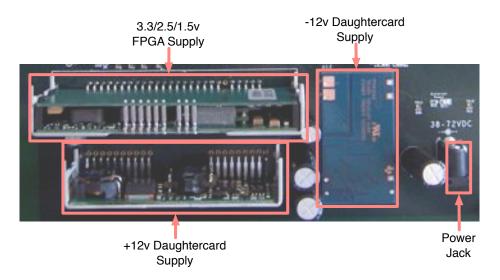

| В.3 | External power and voltage regulators            | 83 |

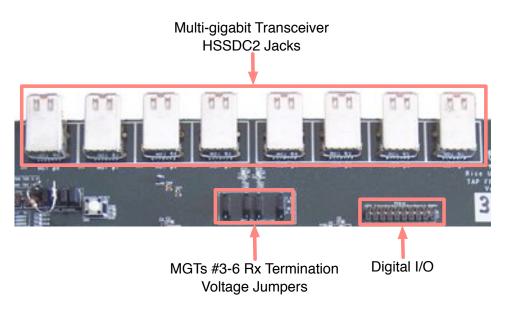

| B.4 | MGTs and digital I/O                             | 84 |

|     |                                         | viii |

|-----|-----------------------------------------|------|

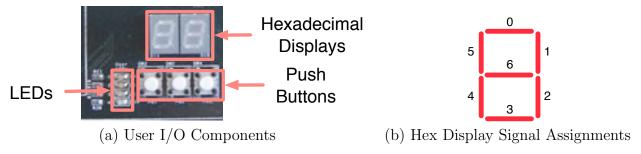

| B.5 | User I/O                                | 86   |

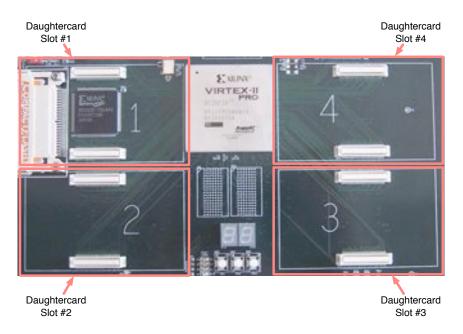

| B.6 | Daughtercard slots                      | 88   |

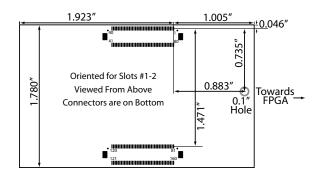

| B.7 | Daughtercard dimensions and orientation | 88   |

# List of Tables

| 3.1 | TAP baseband FPGA resources                        | 34 |

|-----|----------------------------------------------------|----|

| B.1 | Daughtercard and TAP Radio Board FPGA Pin Mappings | 91 |

| B.2 | User I/O, SystemACE and Clock Pin Mappings         | 95 |

| В.3 | SRAM #1 Pin Mappings                               | 96 |

| B.4 | SRAM #2 Pin Mappings                               | 97 |

# Chapter 1 Introduction

As the demand for higher performance wireless communications continues to grow, novel algorithms have been developed which provide increased performance and efficiency. One such class of algorithms involves the use of multiple antennas on either end of a wireless link. Many of these multiple input multiple output (MIMO) algorithms offer impressive performance gains over their single antenna counterparts.

While the development of MIMO algorithms has received substantial attention by the research community, much less time has been spent studying the practicality of implementing such algorithms and evaluating their real-world performance. This neglect is due largely to the substantial processing resources required to implement wideband MIMO algorithms in real-time. Outside of corporate research labs, very few testbeds exist which provide processing resources of sufficient size and flexibility to develop, prototype and evaluate MIMO algorithms.

The need for platforms for prototyping wireless communications systems is not new. A variety of other testbeds have been constructed in recent years for exploring multiple-antenna algorithms. Two of these testbeds are briefly described here to provide some background on our motivations for constructing our own.

One such testbed was designed at the University of Texas' Wireless Network and

Communications group[1, 2]. This testbed is built entirely from commercial off-the-shelf hardware, mostly from National Instruments. It provides resources for half-duplex operation at RF up to 2.7 GHz with two transmit and two receive antennas. Embedded PCs are used for baseband processing with algorithms implemented in LabVIEW. Processing and memory limitations prevent real-time operation; data bursts are limited to around 200ms in length with each burst requiring four seconds of processing at the receiver. This duty cycle permits fairly long transmissions (relative to packet sizes in wireless LAN standards), but clearly falls far short of real-time.

Another testbed was built at UCLA and has been used to implement and evaluate a wide variety of MIMO algorithms[3]. This testbed supports up to three transmit and four receive antennas. It operates in real-time at an RF of 220 MHz with a bandwidth of 4kHz. The testbed hardware is a combination of custom RF hardware and commercial equipment for baseband processing. This testbed has been used to evaluate the performance of a large number of space-time algorithms in real wireless environments[4].

Each of these testbeds, and others like them, provide some of the resources we view as necessary for prototyping wideband MIMO algorithms. Neither one, nor any other testbed we could find, addresses all of the requirements we identified for highly flexible, real-time, wideband MIMO prototyping. This thesis presents two testbeds designed to address all of these needs. The first testbed, discussed in chapter 2 was

constructed first and is built entirely from commercial off-the-shelf hardware. The second testbed, discussed in chapter 3, consists entirely of custom hardware designed as part of the Transit Access Point project[5, 6]. The design, hardware choices, capabilities and application examples for both testbeds are described in detail.

# Chapter 2 Off-the-shelf MIMO Testbed

#### 2.1 Introduction

We present in this chapter a testbed designed for the development, implementation and evaluation of MIMO wireless algorithms. In the interest of building the testbed rapidly, it is constructed entirely from commercial off-the-shelf hardware. The testbed provides hardware for baseband processing, up and downconversion to RF and emulation of multiple wireless channels. It was designed to provide sufficient flexibility to implement a wide range of algorithms while preserving the ability to evaluate an algorithm's resource and power requirements for real-time operation. The testbed hardware and configuration options are discussed here, along with a demonstration of its functionality.

## 2.2 Testbed Design

The testbed consists of hardware which performs three major functions: baseband processing, conversion to and from radio frequencies and emulation of realistic wireless channels. The components we chose to fill each role are discussed below.

#### 2.2.1 Baseband Hardware

One of the major challenges in designing a testbed capable of real-time wideband wireless communication is choosing baseband hardware. We first identified the major requirements the baseband hardware must meet. First, it must possess sufficient processing power to implement a wide variety of complex algorithms. Reliable wireless communication alone is a computationally intensive task; the added complexity of multiple transmit and receive antennas significantly increases the computational requirements. The hardware must also allow reliable measurement of resource utilization and power consumption on a per-algorithm basis. This is an important requirement as the computational requirements of a particular algorithm play a large role in gauging its suitability for real-world use.

We found early on that of all the options for baseband processing, FPGAs provided the greatest flexibility in algorithm design and visibility of resource utilization. We acknowledge that FPGAs may not be ideal for deployment in large scale wireless systems. They are, however, very well suited for use in a rapid prototyping and research environment such as this testbed.

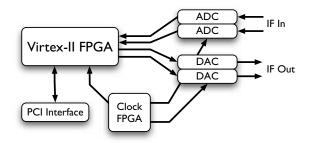

We decided on FPGA-based development systems designed by Nallatech of Glasgow, Scotland as the baseband processing platform. As shown in Figure 2.1, each board houses a multi-million gate Xilinx Virtex-II FPGA and two channels each of analog-to-digital and digital-to-analog conversion. The board's ADCs and DACs are fast enough to connect directly to the intermediate frequency interfaces on the testbed's RF hardware. These connections allow each board to potentially act as a dual-antenna transceiver. Each board also contains a smaller FPGA dedicated to

providing clocks to the larger FPGA and the external analog interfaces. This feature provides a great deal of flexibility in connecting to hardware from different designers with various interface requirements. Finally, the Nallatech board is also a PCI card, providing a high throughput connection over which a host PC can provide and receive data and monitor system performance.

Figure 2.1 FPGA-based processing board

#### 2.2.2 RF Hardware

This testbed is designed for wideband wireless communication in the 2.4 GHz ISM band. The RF hardware must not be tied to any particular standard and must have intermediate frequencies within the sampling capability of the FPGA baseband platform. We also desired control over the synchronization of the frequency translation stages of the radios. Such control allows variation in the carrier frequency offsets between antennas and will prove useful in characterizing the performance of multi-antenna carrier recovery schemes. It also allows offsets between the carriers of multiple transmit or receive antennas to be eliminated entirely, a useful option when

testing algorithms lacking carrier recovery systems.

We decided on 2.4 GHz RF hardware from National Instruments. NI has only recently ventured into the RF hardware market, but we found that their hardware fit the needs of the testbed very well. These devices operate with an intermediate frequency of just 15 MHz, easily within range of the FPGA baseband's sampling capabilities. They also support signal bandwidths up to 20 MHz, accommodating a large variety of wideband schemes.

In order to maximize flexibility in choosing multiple antenna configurations, the testbed also uses a number of RF multiplexers. These devices form the interconnect between the RF transceivers and the channel emulators, described in section 2.2.3. The multiplexers allow most configurations to be implemented programmatically without any changes to the equipment's physical connections. This both minimizes the risk of damage to the equipment and allows for a great deal of automation in switching between interconnection configurations.

#### 2.2.3 Wireless Channel Emulation

Another significant challenge in designing this wireless testbed was identifying some means by which we could provide a realistic wireless channel in a laboratory setting. We required the ability to simulate a wide variety of channel conditions, including fading, multi-path effects and delay spread. We also needed to assure repeatability of experimental conditions, a virtually impossible requirement when

using real wireless channels.

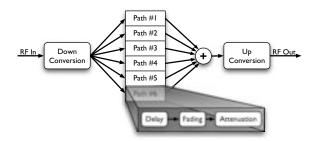

To fill this need, we chose RF channel emulators from Spirent Communications. Each device is capable of emulating two wireless channels, each with six independently configured paths. Figure 2.2 illustrates the capabilities of each emulated wireless channel.

Figure 2.2 Emulated wireless channel

Figure 2.3 Testbed connectivity for half-duplex testing

The emulator can apply one of many fading models, including Rayleigh, Rician and Nakagami, plus programmed delay and attenuation to each path. This flexibility

allows the emulation of a large number of realistic line-of-sight and multi-path environments. The emulator can also introduce arbitrary frequency shifts to each path, providing a reliable means by which to simulate the Doppler effects of various mobile scenarios.

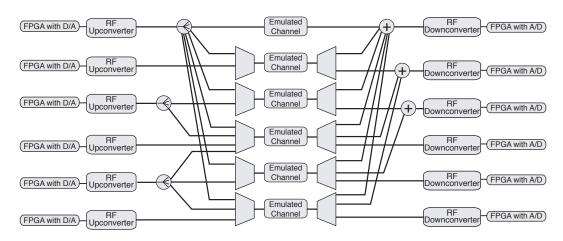

The testbed currently houses three such emulators, providing a total of six independent emulated channels. This fairly large number of channels provides significant flexibility in designing test configurations. In terms of transmit-to-receive antennas, the testbed can implement half-duplex systems of 6-to-1, 3-to-2, 2-to-3, 1-to-6 or any smaller configuration requiring six or fewer channels. Figure 2.3 illustrates the full connectivity for multiple-antenna half-duplex testing.

## 2.3 Application Example: Alamouti Space Time Block Code

Alamouti's transmit diversity scheme was the first example of a space-time code which requires only linear processing at the receiver. Previous space-time coding schemes used trellis based processing. While they provided substantial gains in a wireless communications system, these trellis-based coding schemes were much more complicated to implement than the scheme proposed by Alamouti. This lower complexity makes Alamouti's scheme an ideal candidate for real-world implementation.

The simplest case of Alamouti's scheme utilizes two transmit antennas and one receive antenna. Alamouti included a generalization of his scheme to an arbitrary number of receive antennas, and others later extended his work to include an arbitrary

number of transmit antennas [7]. While we present an implementation of the 2-to-1 scheme here, many of the challenges we faced and the solutions we devised would be applicable in more complex systems.

The remainder of this chapter is organized as follows. Section 2.3.1 describes some of the general challenges in implementing a multiple-antenna communications system in real hardware. Section 2.3.2 discusses in detail the development and design of the system. Finally, the verification of the full system using the testbed equipment is described in Section 2.3.3.

#### 2.3.1 Implementation Challenges

#### Transmitter

The inclusion of an Alamouti encoder in a transmitter design does not significantly increase its complexity. In fact, the hardware realization differs very little from the implementation of two standard wireless transmitters. The only operation the Alamouti encoder performs on modulated symbols is the negation of either the real or imaginary part of a symbol. For most constellations, this processes is analogous to mapping one symbol to another valid symbol. The output of the encoding process is two streams of modulated symbols. Each stream can be fed to identical transmit chains each driving a separate antenna.

#### Receiver

The implementation of an Alamouti receiver is somewhat more challenging. Some of these challenges stem from assumptions made in the original development of this space-time coding scheme. First, the receiver is assumed to have perfect knowledge of every channel between its antennas and those of the transmitter. Such perfect channel knowledge is often assumed in the process of developing wireless algorithms but is rarely available in practice. As a result, an Alamouti receiver must include some mechanism for channel estimation. Further, this coding scheme requires that the channels remain static for the entire duration of two symbol transmissions. This is a fair assumption in some wireless scenarios but is unlikely in many others. Finally, even if the channel conditions change only every other symbol period, it is difficult for the receiver to have knowledge of the changes at such a rate.

Another challenge in implementing the receiver is compensating for carrier frequency offsets. This is a well understood problem in single antenna systems, and many schemes have been developed to deal with such offsets. In a multiple antenna system, however, carrier offset recovery can be much more complicated. First, many carrier recovery schemes are built around phase detectors which estimate the difference in phase between a received signal and a valid modulation symbol. This approach breaks down in the case of transmit diversity systems as multiple symbols arrive at the receiver simultaneously, significantly increasing the number of valid received sym-

bols. As a result, the carrier recovery system must detect phase errors relative to this expanded set of received symbols. The carrier recovery scheme must also compensate for the potential ambiguity resulting from the system locking to the phases of any of the valid received symbols.

A final challenge in the receiver not described in Alamouti's original paper [8] is the recovery of symbol timing. The receiver must determine the frequency and phase of the transmitter's symbol clock based only on the received signal. Like carrier recovery, this is a well understood problem in the single antenna case. Fortunately, most of these approaches are applicable in the case of multiple antennas as well. One complication not addressed by single antenna timing recovery schemes is the potential for different delays experienced by signals traversing separate channels from independent transmit antennas to the same receiver. Rather than modify the timing recovery system to address this, the difference in delays can be modeled as a phase offset imposed by the channel and dealt with in the process of channel estimation.

#### 2.3.2 Implementation Results

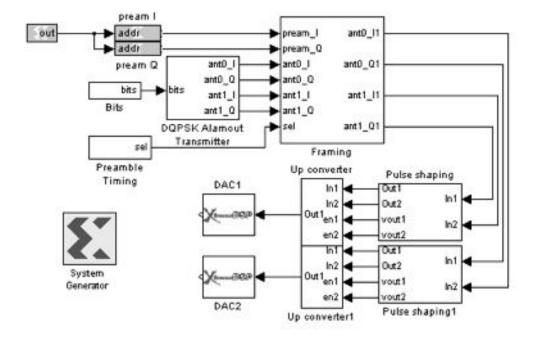

As described above, the implementation of a transmitter with Alamouti encoding does not present any significant challenges. The transmitter combines differentially encoded QPSK modulation with Alamouti encoding. This system outputs two streams of symbols which are fed to identical transmit chains. Each transmit chain includes a raised cosine pulse shaping filter, upsampling and upconversion to

an intermediate frequency of 25 MHz. This IF was chosen for compatibility with the National Instruments NI5610 RF Upconverter, the transmit radio we chose for testing the system.

The transmitter design was targeted to a three million gate Xilinx Virtex-II FPGA. The design consumes about 20% of the logic resources in the FPGA and runs with a system clock of 100 MHz. It should be noted that there are variety of optimizations that could significantly reduce the resource requirements of the transmitter design and that 20% of a three million gate FPGA should be considered an upper bound. A block diagram of the transmitter is shown in Figure 2.4.

Figure 2.4 System Generator model of Alamouti transmitter

The implementation of an Alamouti receiver was far more challenging. The receiver was designed to interface to an NI5600 RF Downconverter, the device used to translate down from RF to an IF of 15 MHz. Samples of this signal are fed to the FPGA at 60 MHz. The FPGA implements a quadrature downconverter to convert the received signal to baseband. This signal is then downsampled to two samples per symbol and fed to the remaining receiver logic. A block diagram of the complete receiver is shown in Figure 2.5. The functionality and design of each block is described below.

Figure 2.5 System Generator model of Alamouti receiver

#### Symbol Timing Recovery

The first receiver block following downsampling is a system for recovering symbol timing as described above. This system must choose the optimal time to sample the incoming symbol stream based only on a local estimate to the transmitter's symbol clock and the received data itself. The FPGA cannot modify the frequency of the oscillator providing its clock signal, so any offset relative to the transmitter's clock must be addressed digitally in the FPGA itself.

We chose to use the symbol timing recovery scheme described in [9]. Specifically, the system utilizes an eight branch interpolating polyphase matched filter. Each of the branches represents a different delay ranging from 0 to 7/8 of a sample period. For each received sample, the timing recovery system must decide which of the eight branches provides the best estimate of the transmitted symbol. This decision is based on an error value calculated by a second polyphase structure implementing the derivative of the matched filter. The optimal sampling time is derived by choosing the polyphase branch which minimizes the magnitude of the derivative filter's output. The details of this approach are discussed in [9] and [10].

The primary reason we chose the timing recovery scheme based on a polyphase filter is the efficiency with which it can be realized in hardware. Most illustrations of this scheme show discrete filter blocks for each polyphase branch. In practice, only one of these branches is used during any one sample period. As a result, the entire polyphase filter can be implemented using a single filter block whose coefficients are reloaded in response to changes in the desired polyphase branch. The only complication to this approach is the requirement that the coefficients be reloaded fast enough that a stream of samples can be processed without interruption.

The receiver implements these filters using multiply-accumulate structures. Each filter uses a single multiplier, accumulator and memory block for coefficient storage. Each polyphase branch has eight filter taps, requiring the filter block to run at eight times the input sample rate. With each input sample, the timing recovery control logic specifies which of eight sets of coefficients should be used to process it. The coefficients for all eight sets are stored in the memory block, so the task of reloading coefficients becomes the much simpler one of indexing into the memory. This approach eliminates any latency in switching branches.

Once the timing recovery system has locked and is tracking the frequency and phase of the transmitter's clock, it will eventually traverse all eight branches of the polyphase matched filter. When the polyphase branch index rolls over from seven to zero (or zero to seven, depending on the sign of the frequency offset), it has effectively repeated or skipped an input sample. Many receiver designs operate at N samples per symbol to accommodate some algorithms, frequently equalizers, which require the extra information. Eventually the receiver must choose which of the multiple samples to use for detection and decoding. This selection process is complicated

by this stuffing or skipping of samples as it must account for the missing or extra sample. Further, every  $N^{th}$  skipping or stuffing of a sample effectively ignores or repeats a symbol. This complicates the Alamouti decoding process as it expects to operate in parallel on a pair of symbols received in series, and the elimination or repetition of a symbol upsets this paring.

The receiver, which operates at two samples per symbol, includes logic to detect when the polyphase branch index rolls over. With each roll over, this logic directs the downstream sample selector to swap its parity. With every other roll over, the Alamouti decoder is directed to jump forward or back one symbol in order to keep transmitted symbol pairs together. This process inevitably introduces errors to the received bits, either by repeating bits or skipping them altogether. Fortunately, this happens with such infrequency that its effects are minimal. With separate FPGAs implementing the transmitter and receiver, each driven by an independent 60 MHz oscillator, we observed the stuffing or skipping of symbols no more frequently than four times per second, or once per million transmitted symbols.

#### Carrier Recovery

The next major function performed by the receiver is to compensate for an offset in the carrier frequencies at the transmitter and receiver. We assume that the carriers from the two transmit antennas have exactly the same frequency and are in perfect phase at the transmitter. In real hardware, this assumption translates to multiple radios sharing a common reference clock. Fortunately, this is realistic in most systems, including the one in which we tested this design. Given this assumption, the receiver needs to compensate for just the offset between the transmitted carrier and the local estimate used for downconversion.

Like timing recovery, carrier recovery is a well studied problem in single antenna systems. As discussed above, the use of multiple transmit antennas complicates the process somewhat. The system uses two transmit antennas and QPSK modulation. As a result, the receiver must recognize one of nine valid sums of two QPSK symbols. Eight of these valid sums are non-zero, meaning the carrier recovery system must measure the phase error to one of eight valid phases.

Figure 2.6 Carrier recovery phase error estimation function

The most obvious method for measuring this phase error is to calculate the arct-

angent of the received symbol. While the CORDIC algorithm provides a method to implement such a function in hardware, such implementations tend to be resource intensive and suffer high latencies in computing results. Instead, we extended the must simpler phase error estimator used in a Costas loop to accommodate the expanded selection of valid phases the receiver must recognize. This new detector calculates a value proportional to both the phase error of a received symbol and the symbol's magnitude. This latter proportionality is important because of the potential for the transmitter to send two symbols which sum to zero. In this case, the only value seen at the receiver will be noise. Any phase error estimate in this case should not be allowed to significantly impact the carrier recovery process. A plot of the function which the phase error estimator implements is shown in Figure 2.6.

The output of this new phase detector feeds a standard 2nd order loop filter which can track both phase and frequency offsets. The output of the loop filter is used to adjust the phase increment of the front-end IF downconverter, eliminating the need for a second digital synthesizer and complex multiplier. This carrier recovery scheme will lock to one of eight phases, offset from the transmitted phase by a multiple of  $\frac{\pi}{4}$ . The orientations which are rotated a multiple of  $\frac{\pi}{2}$  will produce constellations identical to the case of no phase difference. These four orientations will produce symbols which, by means of differential encoding, can be successfully decoded and demodulated. The remaining four orientations, each offset  $\frac{\pi}{4}$  from one of the previous

four, will produce a constellation which appears rotated  $\frac{\pi}{4}$  from the valid nine point constellation resulting from two transmitted QPSK symbols. Symbols received in this orientation cannot be successfully decoded and demodulated. Instead, the receiver detects whether it has locked in one of these states and forces a  $\frac{\pi}{4}$  rotation of its phase lock.

Parts of this carrier recovery scheme would break down in cases where higher order modulation or additional transmit antennas were used. In such cases, the direct calculation of the received symbol's phase by means of a CORDIC arctangent would likely be justified. Alternatively, a frequency-locked loop could be used at the receiver's front end to eliminate an offset in carrier frequency, but not phase. Because such loops are not data-driven, they can be designed independent of modulation schemes or the number of antennas at the transmitter. The receiver would then only need to compensate for a nearly constant phase offset.

#### Channel Estimation

The next block in the design is channel estimation. Alamouti's original algorithm assumed the receiver had perfect knowledge of the channels to each transmit antenna. In reality, the receiver can only estimate the channel conditions. While there has been a great deal of work in designing advanced channel estimation algorithms, we chose to implement a fairly simple scheme in the first revision. The receiver relies on a periodic training sequence that must be inserted into the symbol stream at the transmitter.

The receiver detects this training sequence and correlates the received version against a local copy. This correlation process provides estimates of both channels; these estimates are then used to weight the received symbols and decode the transmitted data.

The channel estimator must listen for the expected training sequence and for one in which the order of symbols in each pair are swapped. This swapping results from the potential ambiguity introduced by the carrier recovery system. If the system locks  $\frac{n\pi}{2}$  out of phase from the transmitter, the order of decoded symbols will be effectively swapped. The channel estimator must detect either the standard or swapped training sequence and include the necessary correction factor in the channel coefficients it provides to the decoder.

#### Decoding & Demodulation

Given two received symbols and estimates of both channels, the Alamouti decoding process is actually very simple. It produces output symbols by using the channel estimates as weights in combining the received symbols. The only complication is the required compensation for skipped or repeated symbols resulting from the timing synchronization process. This compensation is implemented as a three stage shift register which stores incoming symbols. The decoder nominally uses the value stored in the second register but can switch to either the first or third stage as directed by the timing recovery system. This switching allows the decoder to stay aligned to the

proper symbol pairing as produced by the transmitter.

The output of the Alamouti decoder is a pair of symbols which began as valid QPSK constellation points. The demodulator first implements the inverse of the transmitter's differential encoding, then demodulates the data by simply thresholding the real and imaginary parts of the complex symbols.

#### Resource Consumption

The receiver was also implemented in an XC2V3000 FPGA. The full receiver requires just 25% of the logic resources in the FPGA and runs at 60 MHz. At this clock frequency, the receiver achieves a throughput of 7.5 Mb/s.

#### 2.3.3 Verification

Both the transmitter and receiver designs have been synthesized and tested in FPGA hardware. In order to test their functionality, we used the models to establish an end-to-end wireless link. The hardware used for this verification is part of the multiple antenna wireless testbed described in [11]. This tested consists of FPGA hardware for implementing baseband algorithms, wideband radio hardware for translation to RF and channel emulators for simulating various wireless channel conditions. All stages of the testbed are designed to operate in real-time, allowing the design and evaluation of high-throughput, wideband communications schemes.

The FPGA resource utilization for the two models are discussed above. We were

able to establish a connection with a sustained throughput of 7.5 Mb/s operating at 2.4 GHz. Separate FPGA boards were used for the transmitter and receiver, and no connections existed between the boards aside from the wireless link. With no common reference clock, there was a definite offset in the symbol timing and generated carriers between the two systems. This offset allowed the verification of the synchronization and carrier recovery loops, both of which locked and tracked for extended periods.

# Chapter 3 Transit Access Point Platform

#### 3.1 Introduction

This chapter presents the custom hardware platform designed for the transit access points project. The objective of the TAPs project is to design, analyze, prototype and experimentally study the theoretical underpinnings for a wireless internet that simultaneously achieves deployability, scalability, high performance and a cost-effective model. A core building block will be what we call wireless transit access points. A transit access point is a wireless base station with two major features. First, like any standard base station, it provides wireless data services to mobile users. Second, and more importantly, a TAP is capable of high speed wireless links to other TAPs. These connections utilize multiple antennas at each end to dramatically increase the spectral efficiency and throughput of the link. Such TAP-to-TAP links are designed to supplement, or even replace, the wired network infrastructure usually required when deploying wireless data systems.

The ambitious goals of the TAPs project impose certian requirements on the hardware design. These requirements, discussed in the next section, motivated nearly all the design decisions as described in sections 3.3 and 3.4. And although the hardware was designed to prototype and deploy the algorithmic underpinnings of the TAPs project, the platform is flexible and capable enough for use in a wide variety of applications. A few such applications are discussed in section 3.5.

## 3.2 Platform Requirements

The design of a TAP must support its use in a variety of situations in which it must provide a variety of services. This is clear in the network illustrated in Figure 3.1. In this example, most TAPs provide connectivity to mobile users in its vicinity. Some TAPs rely on high-speed wireless links for their own connectivity (B & C, for example). Other TAPs have wired connections to a larger network infrastructure (A & D) but must share this connectivity with non-wired TAPs. Finally, some TAPs must act as wireless routers (C), providing network connectivity by multi-hop networking to other access points which cannot directly communicate with a wired node. The hardware design of a TAP must provide all of these capabilities.

Figure 3.1 Example transit access point network

#### 3.2.1 Wireless Interfaces

One of the fundamental premises of the TAP design is its being equipped with multiple radios and antennas which can be used in unison for spectrally efficient links at very high data rates. This requires that the hardware design provide a means for multiple radios to be driven by a common baseband processor. Further, the physical layer design for TAP-to-TAP links will be entirely custom and will likely not be interoperable with any existing system. Thus, a TAP's radios must be capable of wideband operation in order to support the spectral requirements of these high throughput links but cannot not be tied to any particular standard.

Another requirement imposed by the capabilities described above is the need for multiple air interfaces. An air interface is defined here as the logical abstraction of multiple radios and antennas which act together to communicate over a single link. The number of air interfaces required will vary depending on what services a particular TAP is expected to provide. For example, a TAP which provides connectivity to mobile users and uses a high speed wireless link for its own network connection would need at least two interfaces. A TAP at the core of a network which shares its wired network connection with many other non-wired nodes would need many more.

#### 3.2.2 Processing Resources

The other fundamental requirement of the TAP hardware is the need for sufficient processing power to implement advanced multiple antenna wireless communications algorithms. This requirement poses a kind of cart-before-the-horse problem in that many of these algorithms are still being researched. This is especially true for TAP-to-TAP links, whose physical layer design has only recently been started. Consequently, the TAP hardware design should provide as much processing power in as flexible way as possible. Further, it should support some means of supplementing these processing resources should the base design prove insufficient.

#### 3.2.3 Flexibility

A final requirement of the TAP platform is flexibility. This requirement is imposed by the wide variety of scenarios in which a TAP must operate. This is well illustrated in the example TAP network shown in Figure 3.1. In this example, only a few TAPs have wired network connections. Some TAPs act as routers for neighboring access points while others provide access only to mobile users. Finally, some TAPs utilize multiple TAP-to-TAP links while others require just one. Clearly the TAP platform must be very flexible, able to provide whichever capabilities are required at a particular node in the network.

### 3.3 High-level Design Decisions

#### 3.3.1 Custom Hardware

One of the earliest and most basic decisions was the choice to design custom hardware for all the major components of the platform. This may seem an odd decision, given the existence of the earlier MIMO testbed described in chapter 2. However, in the early stages of defining the requirements of the TAP platform, it became clear that neither the earlier testbed nor any commercial platform we knew to exist would be suitable. The TAP platform requires substantial baseband processing resources which are tightly coupled with multiple radios, repliacted many times to form a TAP network. The bulk, cost and limited extensibility of the original testbed equipment meant it simply could not be used to construct TAPs.

The primary drawback to the custom hardware approach is the enormity of the design effort. We had never attempted to design boards as complex as the two described later in this chapter. However, it was clear that the benefits of a design customized to the exact needs of the TAP platform justified the effort and risk involved.

#### 3.3.2 Core Components

As mentioned above, the TAP baseband algorithms are not yet defined. Dedicated baseband processors are available for a wide variety of wireless networking standards, but such devices are not suitable for implementing the custom algorithms in a TAP. The device that provides the baseband processing must therefore be very

flexible. Further, these baseband algorithms are expected to be very complex, requiring significant processing resources. The baseband processor must be tailored to the DSP-intensive operations, such as filtering and correlation, which are common in communications algorithms. Finally, the processor must be capable of highly parallel operation in order to realize the bandwidth and throughput goals for a TAP.

Next, the TAP baseband processor connects to multiple radios, each of which communicates via a wideband analog interface. Once digitized, each analog interface will require a high throughput, high precision, digital connection to the baseband processor. Consider a TAP's baseband processor controling four radios and each radio has a analog complex baseband interface (e.g. separate I/Q analog signals) with a bandwidth of 20 MHz. The resulting sustained throughput requirements for the baseband processor exceed 300 MB/s in each direction. This is a substantial requirement, generally exceeding the capabilities of processors whose primary off-chip interfaces are standard memory busses.

It became clear very early in the design process that FPGAs were the only devices which could practically meet all of these requirements. Large FPGAs provide tremendous amounts of processing power, all of which, by definition, operates in parallel. All of an FPGAs interfaces to external devices also operate in parallel, significantly easing the aggregate throughput requirement discussed above. FPGAs are also extremely well suited for DSP-intensive operations. For example, large devices include

more than 300 dedicated multiplier blocks, all of which can be used simultaneously.

Once FPGAs were chosen as the baseband processor, a radio had to be selected. Two options were considered here. First, it would be possible to design a radio from discrete components, implementing all of the necessary mixing, filtering and amplification in a custom circuit. Such a design would provide a completely generic analog interface and could be tailored to the desired bandwidth and radio frequency specifications. Unfortunately, the design of such a system is a very challenging undertaking which falls well outside the expertise of anyone involved with this project. Instead, a third-party radio transceiver was identified which meets the TAP radio requirements, the specifications of which are discussed below.

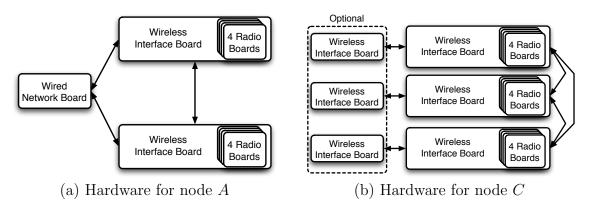

#### 3.3.3 Hardware Partitioning

A final high-level design decision involves the partitioning of a TAP into multiple boards. In general, a TAP will have a minimum of three air interfaces, each equipped with four radios. Some TAPs will also have wired network connections in addition to their wireless interfaces. Assuming each wireless interface will require at least one FPGA, a TAP will consist of at least three large FPGAs plus 12 radios. Designing a single board with all of these components would be risky and very expensive. Instead, a TAP's functionality is divided across three boards. The first is a simple radio board, containing a single RF transceiver and the necessary analog-digital conversion. The second board hosts the large baseband FPGA and has slots for four radio boards. This

board provides the TAP with a single air interface. Finally, a third board contains a smaller FPGA with a wired network interface. This division of hardware seems natural but poses the significant problem of designing some means to interconnect the boards. The wireless interfaces in a TAP will need to communicate with both the wired and other wireless interfaces. Given the high data rates these interfaces are expected to support, this board-to-board communication must be fast and have low latency. Further, an average TAP will consist of four boards, each of which must be able to communicate with every other. As more boards are added to a TAP (e.g. should additional wireless interfaces be required), this problem of interconnection becomes substantially more complicated.

A possible solution for the board-to-board interconnect is a traditional backplane architecture where each board connects to a common, parallel bus. There are a wide variety of standards for such busses, including the various flavors of PCI, which are easily implemented in an FPGA. The problems which plague such architectures, however, would prove especially troublesome in a TAP. For example, the maximum number of boards which can access the bus must be pre-defined when designing the backplane. Additionally, because boards are connected in parallel, they must contend for bus resources. In the worst case, a pair of boards could monopolize the bus, severely limiting the rate at which any other boards could communicate. Finally, the maximum communication rate in most parallel busses is simply too slow for the

high-throughput connections which are required between boards in a TAP.

The solution which was selected for this design is, in many ways, the exact opposite of the bus architecture described above. Instead of having a connections to a common backplane, every board in a TAP is directly connected to every other. This point-to-point topology enables communication between any pair of boards regardless of what resources any other boards are consuming. A fully-interconnected design, however, somewhat complicates the architecture of a TAP. Each board must be equipped with a dedicated connection for every other board in a TAP. Adding a new wireless interface, for example, would consume an additional connection on every existing board. At first a glance, it seems problematic that the resource requirements increase with the number of boards in a TAP. However, if each board could be efficiently equipped with a large number of identical, high speed connections, this architecture is justified. Fortunately, this requirement is easily met in the TAP design, as detailed in the discussion of component selection below.

# 3.4 Hardware Design

This section discusses the low-level hardware design of the TAP platform. The actual design includes a large number of parts, including analog converters, memory and power regulators. Rather than list all the various parts and their individual functions here, the full schematics are included in Appendix A and are available online [12]. Instead, the primary components and key design features of each of the

three TAP boards are discussed.

#### 3.4.1 Wireless Interface Board

Figure 3.2 shows a block diagram of the TAP wireless interface board. Each of its major features is discussed in detail below.

Figure 3.2 TAP wireless interface board

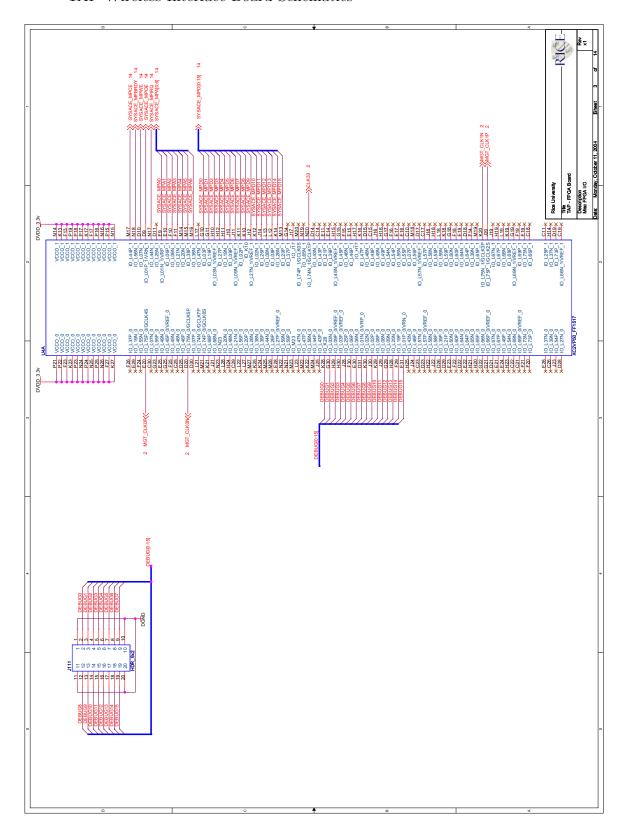

#### **FPGA**

The most important component on the board is the FPGA. The choice of this FPGA for baseband processing is actually fairly straightforward. As described above, this design must provide sufficient resources to implement baseband algorithms which, though not yet defined, are expected to be very complex. As a result, the chosen FPGA should be as large as is reasonably possible. The most advanced FPGAs available at the time of this design are those in Xilinx's Virtex-II Pro line [13]. The

part chosen for the TAP baseband processor is the XC2VP70, the second-largest FPGA in the Virtex-II Pro family.

Table 3.1 summarizes the resources provided by the TAP baseband FPGA. It also lists the resources for a slightly less capable chip, the XC2VP50. This FPGA is pin-compatible with the larger chip; either can be mounted on the wireless interface board as the TAP baseband processor.

|                   | XC2VP50    | XC2VP70    |

|-------------------|------------|------------|

| User I/O          | 852        | 964        |

| Gates             | ≈5 million | ≈7 million |

| Integrated RAM    | 4.2 Mb     | 5.9Mb      |

| 18x18 Multipliers | 232        | 328        |

| PowerPC Cores     | 2          |            |

| Rocket I/O        | 16         |            |

| Price Each        | ≈US\$1700  | ≈US\$2500  |

Table 3.1

TAP baseband FPGA resources

In addition to providing generous logic resources, the Virtex-II Pro baseband FPGA includes a number of additional features which will be critical in the operation of a TAP. The first is the inclusion of multiple PowerPC cores embedded in the logic of the FPGA. These cores are full 32-bit RISC processors whose external interfaces are tied to the device's programmable logic fabric. The TAP baseband FPGA has two such cores which operate independently. These cores are meant to compliment the operation of the FPGA by providing a means to execute pre-existing software

code or to perform other processing which is not well suited for implementation in general logic. It is even possible to run a full operating system in one of the processor cores. Xilinx provides a version of Linux which will boot in the embedded PowerPC and can interact with the custom design implemented in the surrounding logic. This offers the interesting possibility of a TAP being, in essence, a PC with many wireless network interfaces. This abstraction could prove very useful when it comes time to implement higher-layer protocols (MAC, routing, etc.) in a TAP.

#### Multi-gigabit Transceivers

Another feature of Virtex-II Pro FPGAs which is key to the TAP architecture is RocketIO, Xilinx's name for its high-speed serial transceiver technology. These transceivers, generically known as MGTs (multi-gigabit transceivers), enable very high throughput, full duplex connections for chip-to-chip or board-to-board communication. Each transceiver is capable of communicating at 3.125 Gb/s over a four wire serial link. Multiple transceivers can be bonded together to achieve even faster aggregate throughput. The TAP baseband FPGA is equipped with 16 such transceivers, providing significant resources for off-chip communications. Eight MGTs are wired to off-board connectors on the wireless interface board, allowing up to eight boards to be fully interconnected with multi-gigabit point-to-point links when constructing a TAP. These eight MGTs are terminated with Infiniband-keyed HSSDC2 jacks. These jacks are a standard high-speed serial connector, allowing the use of commercially

available cables for connecting TAP boards.

#### Daughtercard Slots

The wireless interface board has four daughtercard slots. Each slot uses two high density, low profile connectors providing a total of 124 digital signals routed to dedicated pins on the FPGA. Each slot is routed to a separate I/O bank on the FPGA, facilitating the efficient allocation of logic resources to each card. In a TAP these slots will be occupied by radio boards (see section 3.4.2). However any board designed with the same interface can fit in these slots. This provides tremendous flexibility in connecting other peripherals and interfaces to the FPGA. One such board, providing fast Ethernet, USB and serial interfaces, has already been designed.

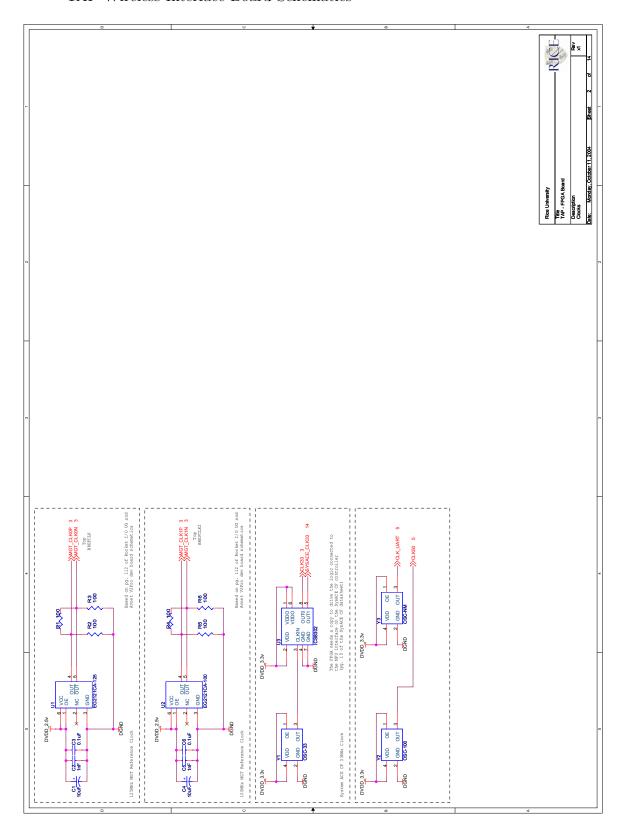

#### FPGA Configuration

FPGAs store their configuration in volatile memory which requires it be downloaded every time power is cycled. Further, the FPGA is not active during this download, so the configuration file must be downloaded on startup as quickly as possible. The size of the configuration file grows with the logic resources provided by an FPGA. For the XC2VP70, this configuration file requires 3.2MB of storage. Thus, the TAP configuration system must provide both high-speed, automatic programming and high storage density for configuration files.

A configuration solution which addresses all of these needs was designed using the

Figure 3.3 TAP FPGA configuration system

Xilinx System ACE CompactFlash chip. This chip is intended specifically for systems requiring rapid in-system configuration and high storage density for configuration files. It has three primary interfaces as shown in Figure 3.3. First, it connects to a standard CompactFlash slot, accommodating the same removable flash cards which are widely available for use in consumer electronics. The CompactFlash card is loaded with configuration files on a PC which, when plugged into the board, are downloaded to the FPGA by the System Ace chip. This download occurs over the System Ace's second interface, a standard JTAG port for target devices. The third interface is a standard microprocessor memory bus between the FPGA and System ACE chip. This interface allows the FPGA to access registers in the System Ace to monitor status or trigger re-configuration. More importantly, this interface provides the FPGA read/write access to the CompactFlash card. This enables two important features. First, the FPGA can overwrite or add new configuration files received over one of its network interfaces, then trigger re-configuration using the new file. In other words, a TAP can be reprogrammed remotely without any physical access. Second, the FPGA can use empty space on the flash card to store any information it requires between power cycles. This includes both board-specific parameters, like MAC addresses and serial numbers, and state information like log files. The CompactFlash card can be removed without interrupting the FPGA, allowing a card filled with log files to be swapped for an empty one on the fly.

The FPGA's JTAG interface can be isolated from the System ACE by removing four jumpers. This is intended to facilitate both hardware debugging and the creation of one long JTAG chain containing every FPGA in a multi-board TAP. When these jumpers are replaced with cables connecting the boards' JTAG chains together, a single System ACE will be able to configure every FPGA in a TAP. This will simplify the process of remotely reprogramming a TAP.

#### **SRAM**

The wireless interface board includes two static RAMs. Each is a 100 MHz 9Mb (36x256k) SRAM wired to dedicated pins in independent I/O banks on the FPGA. The two banks can be used separately or together as a single 72-bit wide memory. These RAMs were included in anticipation of memory requirements beyond what is provided by the FPGA's internal block RAMs. Potential uses include program and data storage for the PPC cores or as packet buffers for the MAC and PHY algorithms. Both RAMs use zero bus turnaround (ZBT) interfaces, allowing one read or write access per cycle without any wait states.

#### User I/O

In order to speed hardware debugging and algorithmic development, the board includes a number of components dedicated to user interface. Three push buttons, four LEDs, two seven segment displays and 16 general I/O are all available for users to interact with designs implemented in the FPGA. Once a TAP is deployed, these components will serve little function and can easily be omitted during assembly. Experience has shown, however, that such user I/O are invaluable during the incremental development and implementation of algorithms on the FPGA.

#### **Power Supplies**

Large FPGAs are capable of consuming very significant amounts of power. The actual power requirements depend heavily on the design implemented in the FPGA. The number of I/O buffers, block RAMs, multipliers, logic slices, processor cores and MGTs used in a design all significant affect the total power consumption. A conservative estimate of the power consumption for a moderately full XC2VP70 exceeds 20 watts[14]. The short term consumption can be even higher, depending on the number of transistors switching in a given clock cycle. These requirements are further complicated by the three different voltage supplies used by the FPGA: 1.5 v for its core, 2.5 v for auxiliary functions and 3.3 v for I/O buffers. The four daughtercard slots also have the potential to consume significant amounts of power. This is especially true

for radio daughtercards whose analog converters, transceivers and power amplifiers all draw significant currents.

The wireless interface board's power system addresses all of these requirements using three power modules from Texas Instruments. The first supplies up to 10 A to each of the three voltages required by the FPGA. The other two are dedicated supplies for the four daughtercard slots, providing +12 v at 30 watts and -12 v and 7 watts. The outputs of all three modules are isolated from the shared 48 v input. The daughtercards do not share the FPGAs supplies. Instead, a daughtercard must regulate its own power from the  $\pm 12$  v supplied through their connectors. As described in section 3.4.2, the analog circuity on the radio board requires very low-noise power supplied by a linear regulator near the circuit. This requirement would be impossible to meet if the power regulators were external to the radio board. The two daughtercard power modules are through-hole components, facilitating their mounting or removal after initial assembly. In some cases, a wireless interface board will be used without daughtercards, utilizing only the FPGA for extra processing resources. The daughtercard power modules can be removed in such scenarios to reduce costs and power consumption.

#### **PCB** Details

The TAP wireless interface board is a 16 layer 8" x 8" x 0.092" printed circuit board. The board was routed entirely by hand in order to maximize signal integrity

by minimizing layer transitions by signal traces. The flexible pinout of the FPGA allowed every signal to be routed using no more than two vias. In other words, every trace on the board is routed on just one or two layers, passing through no more than two layer transitions (generally from the top to an inner routing layer and back). Ten layers are dedicated to signal routing; the remaining six are used for power distribution and ground planes. Controlled impedance is required during fabrication on layer 6 in order to assure the  $100\Omega \pm 5\%$  differential impedance of the MGT traces. The board is manufactured using FR-4 dielectric with 0.005" minimum trace width and spacing. The routing was completed using only through-hole vias in order to minimize fabrication costs\*. There is an extensive network of bypass capacitors, more than 300 in all, mounted on the back of the board. These capacitors provide both paths for signal return currents and local power storage for the FPGA when its short term current requirements vary faster than the power regulators can adapt. The quantity and distribution of values for these capacitors are designed according to recommendations from Xilinx[15]. See Appendix ?? for plots of each layer.

The first revision of this board has been manufactured, assembled, tested and is fully functional. The only error discovered so far is a missing pull-up resistor on one signal. A second revision is planned which fixes this error and rearranges components

<sup>\*</sup>A version of the board was actually completed using just 10 layers and blind vias (holes which do not extend all the way through the board). This version was scrapped when the fabrication costs were quoted at \$6,000 per board, 10x the cost of the final 16 layer version.

for more flexibility in designing daughtercards. Another future revision will likely be designed to take advantage of Xilinx's newer family of Virtex-4 FPGAs.

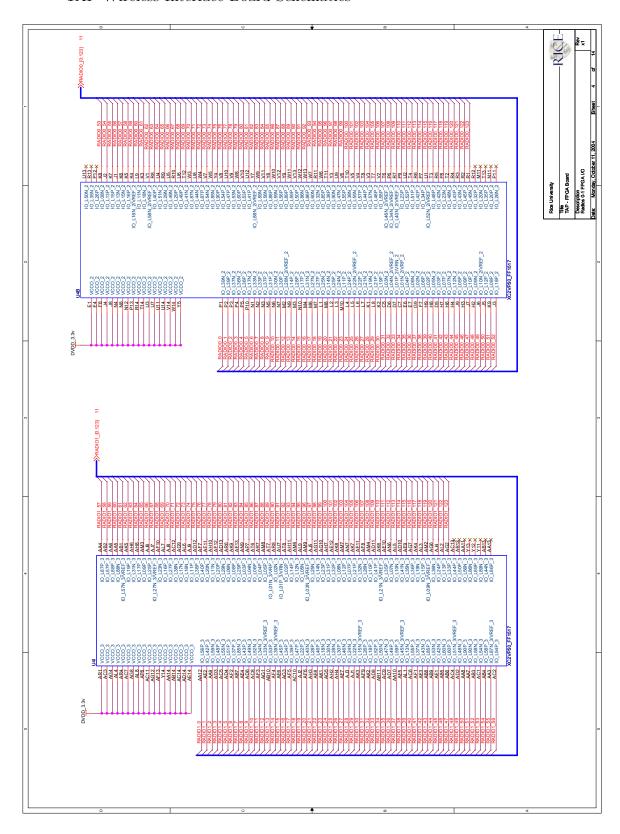

#### 3.4.2 Radio Board

The second core hardware design is the TAP radio board. This board is designed as a daughtercard for the wireless interface board described above. It implements full transmit and receive chains, all the way from the FPGA's digital interface to analog RF. A block diagram of the board is shown in figure 3.4 and its major features are discussed below.

Figure 3.4 TAP radio board

#### RF Transceiver

A radio transceiver suitable for use in this design was to be the most difficult part to choose. The difficulty stems from the scarcity of wideband radio chips which are not tied to a particular baseband processor. A vast majority of wireless networking designs are built to comply with one or more of the IEEE 802.11 standards and provide little flexibility beyond those specifications. A TAP's wireless interfaces, on the other hand, will not use these standards and must be designed to support a multiple antenna physical layer which is still under active development.

Fortunately, a suitable radio chip was recently released which exceeds all of the requirements discussed above. This radio, the MAX2829 from Maxim Integrated Products, is a direct conversion radio transceiver which supports both the 2.4 GHz and 5 GHz ISM bands [16]. Although it is intended for use in 802.11a/b/g/n designs, this transceiver provides a flexible analog baseband interface. This interface allows the translation of any waveform, with a bandwidth up to 40 MHz, between baseband and RF, regardless of the waveform's adherence to an 802.11 standard. Further, when driven by a common reference clock, the phase coherency of the local oscillators in multiple MAX2829 transceivers is guaranteed. This feature is critical in MIMO applications as many algorithms require carefully controlled phase relationships and accurate measurements of phase among multiple antennas.

#### **Data Converters**

The wireless interface board daughtercard connectors provide a strictly digital interface to the FPGA. The MAX2829, however, has an analog baseband interface, consisting of four differential analog signals (I and Q for transmit and receive). The radio board includes the necessary A/D and D/A converters to complete these interfaces. The receive path uses the AD9248 A/D converter. This part is a dual-

channel 14-bit converter which samples at up to 65MS/sec. The sampling rate and input bandwidth both exceed the requirements for operating the MAX2829 in 40 MHz bandwidth mode. The transmit path uses the AD9777 D/A converter. This is a dual-channel 16-bit converter which samples at up to 160MS/sec. The use of dual-channel converters is intended to minimize gain and delay errors which would manifest themselves as I/Q gain and phase imbalances in the transmit and receive paths. A separate 10-bit 20MS/sec A/D converter is used to convert the MAX2829's received signal strength indicator (RSSI) signal. All three converters have parallel digital interfaces connected to dedicated pins on the daughtercard connectors.

#### RF Front End

The TAP radio board's RF front end includes all the components required to interface the MAX2829's RF transmit and receive signals with off-board antenna connectors. The transmit chain primarily consists of passive components for impedance matching and a dual-band power amplifier from Sharp Microelectronics. The amplifier has an output power of +18dBm in both the 2.4 GHz and 5 GHz bands. The receive chain consists of bandpass filters for both RF bands and passives for impedance matching. The two chains are joined by diplexers and a double pole double throw (DPDT) antenna switch. This switch has four ports: a transmit input, driven by the combined 2.4 GHz and 5 GHz RF signals, a receive output, driving a combined 2.4 GHz and 5 GHz signal and two bi-directional antenna ports. This

switch is controlled by the FPGA and allows a variety of configurations for the two antenna connectors. One antenna can be bi-directional at 2.4 GHz with the other used at 5 GHz. Alternatively one antenna can be used in both bands for transmission only with the other antenna for used receiving. Since both the antenna switch and the MAX2829 are controlled by the FPGA, these modes can be selected on the fly without any hardware changes.

The RF front end section of the TAP radio board is based on a reference design provided by Maxim. Part of this reference design is discussed in an application note authored by Maxim engineers[17]; the schematics and layout files are not available for general distribution.

#### Clocking

A variety of clocks are required by the components on this board, all of which are very sensitive to the quality of the clock signals. The data converters require a clock with a strict 50% duty cycle and very low jitter. Further, the clock signals driving each channel in the dual-channel converters must be perfectly synchronized in order to minimize any offsets in the I and Q samples. The reference clock signal provided to the MAX2829 transceiver is used to generate the 2.4 GHz and 5 GHz carriers for conversion to and from RF. Any phase noise in this clock signal will directly translate to the RF signal, potentially reducing noise margins and significantly decreasing performance. Finally, all of these clock signals must be perfectly synchronized across

all the radio boards connected to a common wireless interface board. This is a strict requirement of MIMO algorithms which may operate by applying minor phase offsets between antennas, possible only when a common reference clock is shared by all components.

This complicated clock distribution problem is solved by using a pair of off-board master oscillators and clock distribution chips, one each for the converter and MAX2829 reference clocks. The radio board has two MMCX jacks for receiving these clock signals by coaxial cable. The cables used to route clocks to each radio board can be matched in length, minimizing any skew between the boards. This approach also isolates the clock signals from any digital signals routed on the wireless interface or radio boards, minimizing the potential for coupled noise.

#### Power Supplies

Analog circuits, and RF circuits in particular, require very low-noise power supplies in order to maximize performance. One key way to reduce the noise in analog power supplies is to isolate the supplies for the digital and analog sections of mixed-signal chips. This approach is used on the TAP radio board. A dedicated voltage regulator is used for the digital interfaces on the fast data converters. A separate regulator drives the analog supplies on the converter. A third regulator is used for the MAX2829's supply in order to further isolate the RF chain from potential supply noise. A fourth regulator is dedicated to the supply pins of the transceiver's voltage-

controlled oscillator (VCO). Any noise present in the VCO supply can directly impact the noise floor at RF; the dedicated regulator is used to mitigate this as much as possible. Finally, multiple bypass capacitors of various values are placed adjacent to every power pin on every component to minimize coupled and emitted interference from suboptimal return current paths.

#### **PCB** Details

The TAP radio board is a 6 layer 2.9" x 1.7" x 0.062" printed circuit board. The board was routed entirely by hand in order to maximize signal integrity and adhere to the strict impedance requirements of the RF circuits. It was manufactured with FR-4 dielectric and 0.005" minimum trace width and spacing. Layers 1, 3, 4 and 6 are used for routing signals; layers 2 and 5 are used for power and ground planes. Where not otherwise occupied, all six layers are flooded with copper tied to ground. All analog and RF signals are routed on the top layer where an impedance of  $50\Omega$   $\pm 5\%$  is guaranteed by the board manufacturer. See Appendix ?? for plots of each layer.

#### 3.4.3 Wired Network Board

The final board in the TAP platform provides a wired network connection and will generally be used by TAPs which have direct access to a internet connection. This board is based on a Virtex-II Pro FPGA smaller than the one mounted on the wireless

interface board. This FPGA provides eight multi-gigabit transceivers (MGTs), six of which are dedicated to communicating directly with wireless interfaces in a TAP. The remaining two MGTs are used as gigabit Ethernet connections. The FPGA also provides two PowerPC cores, an ideal resource for implementing the various networking algorithms operating above the MAC and PHY.

The design of this board is currently underway.

Figure 3.5 TAP wired network board

## 3.5 Applications

This section describes some applications for the TAP hardware platform. Though the platform was designed to meet the requirements of a TAP network, it provides sufficient resources and flexibility to be used in many other settings.

#### 3.5.1 Multi-hop Fixed Wireless Networks

This platform was designed to meet the requirements presented in the original TAP proposal[5]. This section describes how the custom hardware designs discussed above can be assembled and utilized to meet this requirements.

Figure 3.6 shows the typical TAP network discussed in section 3.2. In this network the five TAP nodes each perform different functions which require different resources. Node A, for example, has a wired network interface connected to the Internet, a wireless TAP-to-TAP link with node C and provides wireless access to nearby mobile users. Contrast this with node C which acts only as wireless router using three TAP-to-TAP links.

Figure 3.6 TAP network

Figure 3.7 Building TAPs

Though they serve very different functions, both of these nodes can be constructed from the custom TAP hardware. Node A can be built from a wired network board

and two wireless interface boards, one for the point-to-point link, the other for mobile user access. Each wireless interface board would have four radio boards connected in order to provide MIMO capabilities on both wireless interfaces. The three TAP boards would be interconnected by MGTs. This configuraiton is shown in figure 3.7(a). Node C would be built entirely from wireless interface and radio boards. Each of the three wireless interfaces would require its own board, each equipped with four radios. These three boards would be fully interconnected by MGTs. It is likely that the implementation of a full four antenna MIMO transceiver will require more than a single FPGA. Node C would likely need extra processing resources for each wireless interface. The TAP wireless interface board can easily fill this role by simply using it without radios. This scenario is shown in figure 3.7(b). Each secondary processing board would be connected by another MGT to its primary wireless interface board. Should even more processing resources be required, this approach could be extended using additional wireless interface boards interconnected by MGTs.

#### 3.5.2 Real-time Networking Experiments

One of the most promising alternate uses for the TAP platform is in the construction of testbeds for experiments in wireless network algorithms above the physical layer. There has been significant interested in recent years in the empirical evaluation of MAC and routing algorithms in real-world wireless environments. Part of this interest stems from the difficulty in accurately simulating both wireless physical layer algorithms and real wireless channel effects. A number of testbeds have been constructed using standard PCs and 802.11b wireless networking interfaces for the purpose of performing such evaluation [18, 19]. A major drawback to this approach, however, is the limited degree to which the physical and MAC layer implementations can be observed and modified in standard wireless network interfaces. For example, a number of changes to the IEEE 802.11 MAC protocol have been proposed that aim to reduce its overhead and improve its performance [20, 21]. Many of these proposals are supported by simulation results demonstrating performance improvements, but none which requires substantial changes to the MAC is supported by results from evaluation in real wireless environments. This is due largely to academic researchers not having access to a platform with a standard wireless physical layer and programmable MAC. Commercial wireless networking products implement the MAC protocol in an ASIC which, in order to maintain standards compliance certification, must not be modifiable by the end-user. This results in the inability of networking researchers to evaluate the real-world performance of alternate MAC protocols in testbeds built from commercial hardware.

The TAP platform does not suffer this restriction. A TAP wireless interface board with one radio board combined with a standards-compliant physical layer implementation forms a wireless network node with a fully programmable MAC. The MAC could be implemented either in the FPGA's logic resources or in one of its PowerPC

cores. This latter option is particularly useful given that many MAC protocols are already implemented in C for simulation purposes. With some modifications, this code can be targeted to one of the embedded PPC cores where it can interface with the physical layer implemented in the surrounding logic.

Other features of the TAP platform further enhance its use in networking experiments. The nonvolatile storage space provided by the SysateACE CompactFlash interface can be used to store log files and packet traces at each node for offline analysis. Additional wireless interface or wired network boards can be used to provide remote access to a node via an interface independent from the wireless interface under test. And additional radio boards can be added to enable testing of MAC protocols for upcoming MIMO wireless network standards like IEEE 802.11n and 802.20.

# Chapter 4 Conclusions and Future Work

The most significant contribution of this work is the design of the TAP wireless interface and radio boards. These boards are the building blocks for the TAP hardware platform and will play an essential role in the continuing development and eventual deployment of TAP networks. However, a substantial amount of work remains in developing and implementing the algorithms required to achieve the performance goals of the TAPs project. These efforts are already underway, both at the physical and MAC layers. A single antenna OFDM transceiver has been implemented and verified which will form the basis for the full MIMO physical layer. A IEEE 802.11 based MAC implementation targeted to one of the FPGA's embedded PowerPC cores has also been started. These efforts will eventually culminate in the use of a four antenna transceiver, built entirely from the custom hardware described in this thesis, to achieve the aggressive spectral efficiency and throughput goals of the TAPs project.

We fully expect that these algorithmic implementation efforts will expose various strengths and weaknesses of the hardware platform. This, in turn, will drive the development of future revisions of the hardware. We also expect that, in parallel to the TAP implementation efforts, other research groups will begin using this hardware for their own projects. Networking experiments will likely be among the first such

outside applications for the reasons discussed in section 3.5.2. These, and other outside uses of the hardware, will provide valuable feedback for future revisions and extensions of the platform.

# Appendix A PCB Schematics