CM-PLL Clock Module: Connectors

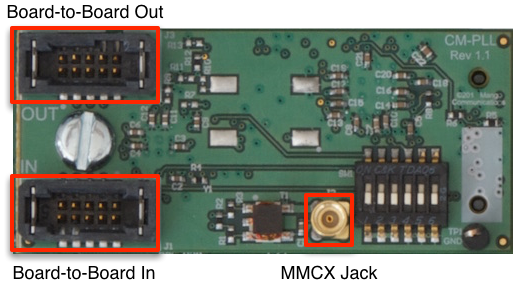

The CM-PLL board has 3 connectors for external cable connections:

- MMCX jack

- Board-to-board Header In

- Board-to-board Header Out

| The WARP v3 board should be powered off before any cables are connected or disconnected from the CM-PLL connectors. The equipment driving the cables should also be powered off when making connections. |

MMCX Jack

The MMCX jack is used to feed a reference clock signal from external equipment, such as test equipment with a 10MHz reference output. This connector is a standard-polarity, standard-gender 50-ohm MMCX jack, also known as a MMCX female connector. The mating cable should have a 50 ohm MMCX plug (male connector).

The MMCX jack feeds a simple circuit which converts the single-ended input signal into a differential signal, which then drives one of the inputs of the reference clock mux. The MMCX reference input can be selected with the appropriate DIP switch setting.

The MMCX reference input presents a 50-ohm load and requires a clock signal amplitude at least 800mVp-p.

The reference designs which use the CM-PLL and w3_clock_controller core assume a 10MHz reference frequency. However the AD9511 PLL can be configured for a wide range of reference frequencies. Refer to the AD9511 datasheet for details on appropriate divider settings for alternate reference frequencies. Custom divider settings can be implemented using the w3_clock_controller custom config feature.

Board-to-Board Headers

The board-to-board headers are designed to support daisy chaining multiple WARP v3 kits equipped with CM-PLL modules. The "In" header dedicates one pin to a reference clock input, selected by the appropriate DIP switch setting. The "Out" header dedicates one pin to a copy of the reference clock signal. This output can be enabled or disabled via via the DIP switch.

Each header also has 4 pins tied to dedicated FPGA I/O. These FPGA pins are bidirectional. User designs can assign the pins whatever function the application requires. The WARPLab reference design, for example, uses the 4 I/O on the "In" header as trigger inputs, and 4 I/O on the "Out" header as trigger outputs.

The 8 FPGA I/O pins routed to the board-to-board headers use 2.5v levels. These pins are not 3.3v tolerant.

The board-to-board headers are 5x2-pin Samtec TFM series connectors, part number TFM-105-02-S-D-WT.

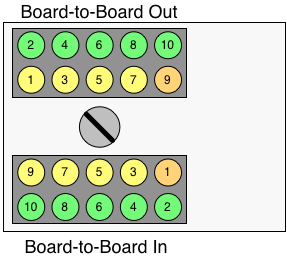

Pinout

The pinout of the two headers is specified below. The figure is oriented the same as the photo above. The pin numbering here matches the Samtec documentation for the TFM connector series. The orientation of the notch in the header shroud is critical. The pin nearest the notch is pin 10.

| In Header | ||

|---|---|---|

| Pin | Function | Specs |

| 1 | Reference Clock Input | Single-ended clock signal, 3.3v max |

| 3 | HDR_IN<0> | FPGA Pin V28 |

| 5 | HDR_IN<1> | FPGA Pin V27 |

| 7 | HDR_IN<2> | FPGA Pin V33 |

| 9 | HDR_IN<3> | FPGA Pin V34 |

| 2,4,6,8,10 | Ground | |

| Out Header | ||

|---|---|---|

| Pin | Function | Specs |

| 1 | HDR_OUT<3> | FPGA Pin W29 |

| 3 | HDR_OUT<2> | FPGA Pin W30 |

| 5 | HDR_OUT<1> | FPGA Pin W34 |

| 7 | HDR_OUT<0> | FPGA Pin V32 |

| 9 | Reference Clock Output | Single-ended clock signal, 3.3v max |

| 2,4,6,8,10 | Ground | |

A cable which connects the Out header of one board to the In header of another board should implement mapping:

| In Pin | Out Pin | Note |

| 1 | 9 | Connects reference clock input to output |

| 3 | 7 | Connects FPGA signal HDR_OUT<0> to signal HDR_IN<0> |

| 5 | 5 | Connects FPGA signal HDR_OUT<1> to signal HDR_IN<1> |

| 7 | 3 | Connects FPGA signal HDR_OUT<2> to signal HDR_IN<2> |

| 9 | 1 | Connects FPGA signal HDR_OUT<3> to signal HDR_IN<3> |

| 2,4,6,8,10 | Mapping is arbitrary - CM-PLL PCB ties all ground pins together | |

Cables

Samtec has many cable options which mate with the TFM series headers. We have tested cables from the FHSC and SFSD series with the CM-PLL module.

FHSC Series The FHSC series cable assemblies use a flat ribbon of 50-ohm coaxial cables, with one cable per pin. The CM-PLL headers are compatible with either the end-launch or right-angle version of the FHSC cables. We recommend cables with right-angle connectors. The part number for this cable is FHSC-105-XX.XX-SBR-SBL-3, where XX.XX is the cable length in decimal inches.

SFSD Series The SFSD series cable assemblies use discrete wires for each signal. These wires are not bound into a single cable, though this is easy to do yourself with tape or zip ties. The compatible part number is SFSD-05-28-F-XX.XX-DR-NUS, where XX.XX is the cable length in decimal inches.

The TFM headers on the CM-PLL are 0.50" pitch, 2x5 pin connectors. These are standard dimensions - there are likely additional cables from Samtec and other manufacturers which are compatible with the CM-PLL headers. If you opt for a different cable, ensure the cable maps signals as specified above.