UCSD EXCITE: Early small-scale prototyping research

The numerous benefits of the prototyping-stage in the research process are well known. Apart from the verification of a conceptual idea, the implementation process frequently reveals unexpected real-world issues which would need to be addressed in order to make any new idea conceived feasible in practice.

In 2008 the California Institute for Telecommunications and Information Technology (CalIT2) and Wireless Access Networks Research at Ericsson started work on the EXCITE project. Utilizing the Rice University Wireless Open-Access Research Platform (WARP), the project set out to demonstrate the flexibility of this platform and how it could be used when researching and demonstrating new radio-communications concepts.

With equal resources contributed from both parties, a close relationship was built as the project actively progressed. Researchers at CalIT2 designed, developed, and built a radio physical layer on the WARP board's on-board FPGA fabric while across the Atlantic, higher-layer protocols were developed at Ericsson Research in Sweden and programmed to run on the board's PowerPC CPUs.

In December 2008 the EXCITE project demonstrated a conceptual three-node cognitive relay network at Ericsson's offices in Stockholm. The demonstration, using the radio physical layer and protocols built over the year within the EXCITE project, was repeated again at the 3rd JTRS Science and Technology Forum in January 2009 in San Diego.

The ongoing challenge is to make this type of implementation activity simpler, i.e., to reduce the development cycle time from back-of-napkin-fabric design to FPGA-fabric design. The ultimate goal is to make radio prototyping more accessible to a wider audience. To the parties involved in this project, this would result in better understanding in the science of radio-communications for students in academia, and at the same time yield quicker turnaround times for investigations and demonstrations of new concepts in industry. To this front, researchers at Calit2 have been developing a tool called PaSiVe (Parameterization, Simulation and Verification), which provides a framework for organizing MATLAB and Xilinx System Generator design files to support modular team collaboration to prototype a complex PHY layer on an FPGA.

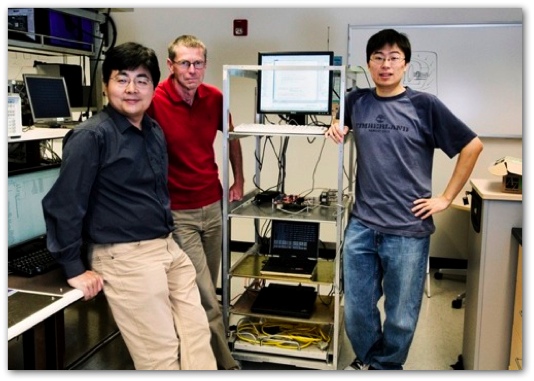

Pictured (left to right): Zhongren Cao (UCSD), Magnus Almgren (Ericsson), and Joshua Ng (UCSD)