| Version 2 (modified by murphpo, 12 years ago) (diff) |

|---|

WARP v3 AD Bridge (w3_ad_bridge)

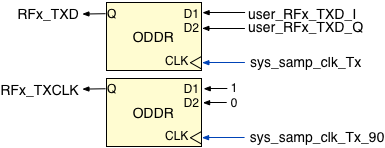

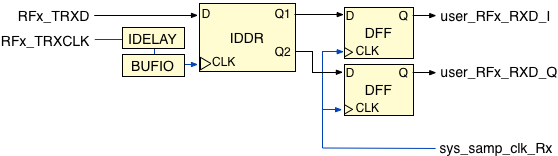

The w3_ad_bridge core implements the I/O logic for interfacing user designs with the digital I/Q interfaces of the AD9963 ADCs/DACs on the WARP v3 board. The AD9963 digital ports are double data rate (DDR) interfaces with interleaved I/Q. The w3_ad_bridge core uses IDDR and ODDR primitives in the FPGA IOBs to efficiently translate between the external interleaved I/Q ports and internal separate I/Q busses.

The w3_ad_bridge core is packaged as a pcore which can instantiated in an XPS project. The design has been tested in hardware using Xilinx ISE 13.4. The w3_ad_bridge core does not attach to a processor bus, so there is no driver.

The current version of the w3_ad_bridge core is v3_00_g.

Tx Path

The w3_ad_bridge Tx path is illustrated below. The logic depicted here is replicated for each RF interface.

External Ports:

| Port | Direction | Width | Connection | Description |

|---|---|---|---|---|

| ad_RFA_TXD | Output | 12 | AD9963 TXD | RF A Tx data (DDR, I/Q interleaved) |

| ad_RFA_TXCLK | Output | 1 | AD9963 TXCLK | RF A Tx data clock |

| ad_RFA_TXIQ | Output | 1 | AD9963 TXIQ | RF A Tx data select |

| ad_RFB_TXD | Output | 12 | AD9963 TXD | RF B Tx data (DDR, I/Q interleaved) |

| ad_RFB_TXCLK | Output | 1 | AD9963 TXCLK | RF B Tx data clock |

| ad_RFB_TXIQ | Output | 1 | AD9963 TXIQ | RF B Tx data select |

Internal Ports:

| Port | Direction | Width | Description |

|---|---|---|---|

| user_RFA_TXD_I | Input | 12 | Tx I samples from user design |

| user_RFA_TXD_Q | Input | 12 | Tx I samples from user design |

| sys_samp_clk_Tx | Input | 1 | Clock for user-supplied TXD signals |

| sys_samp_clk_Tx_90 | Input | 1 | 90 degree phase shifted version of sys_samp_clk_Tx |

Rx Path

Hardware

The MHS snippet below shows the w3_ad_bridge instantiation used in the WARP v3 reference projects.

#Top level ports

Source

The full hardware and software source code is available in the repository: PlatformSupport/CustomPeripherals/pcores/w3_ad_bridge_v3_00_g. The VHDL, Verilog and C source code are made available under the WARP license.

Changelog

2012-Aug-12:

- Created w3_ad_bridge_v3_00_g, branched from w3_ad_bridge_v3_00_f

- Separate sys_samp_clk ports for Tx/Rx paths, to enable different ADC/DAC data rates