Note: As of version 10.1.02, Xilinx has added a stable EDK export flow to System Generator. The new flow creates a PLB46 slave interface with access to registers, FIFOs and shared memory blocks in the user design. This flow completely replaces sysgen2opb and the OPB Export Tool. As a result, these tools are no longer maintained.

sysgen2opb Shared Memory Extension Dual Port RAM Requirements

Invoke the shared memory extenion with the argument 'smon' when calling sysgen2opb:

>> sysgen2opb('myModel', 'smon')

In order to use this extension, your model must contain at least one dual-port RAM configured as described below.

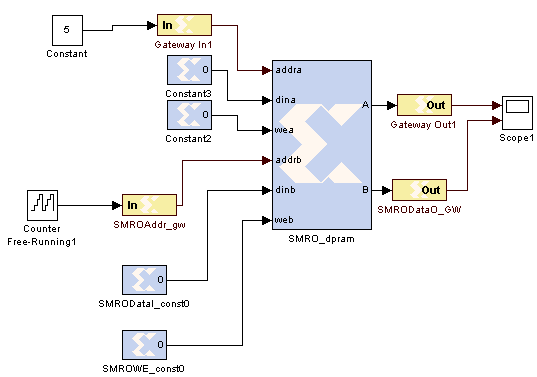

DPRAM (Read only)

DPRAM Name Prefix: SMRO_

DPRAM Inport addrb Source Block

Name Prefix: SMROAddr_

Block Type: Gateway In

Output Type: UFix14_0

DPRAM Inport dinb Source Block

Name Prefix: SMRODataI_

Block Type: Xilinx Constant

Constant Value: 0

Number of bits: 32

DPRAM Inport web Source Block

Name Prefix: SMROWE_

Block Type: Xilinx Constant

Output Type: Boolean

Constant Value: 0

DPRAM Outport B Destination Block

Name Prefix: SMRODataO_

Block Type: Gateway Out

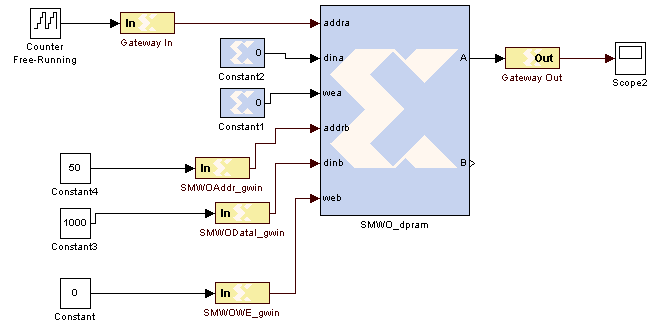

DPRAM (Write only)

DPRAM Name Prefix: SMWO_

DPRAM Inport addrb Source Block

Name Prefix: SMWOAddr_

Block Type: Gateway In

Output Type: UFix14_0

DPRAM Inport dinb Source Block

Name Prefix: SMWODataI_

Block Type: Gateway In

Number of bits: 32

DPRAM Inport web Source Block

Name Prefix: SMWOWE_

Block Type: Gateway In

Output Type: Boolean

DPRAM Outport B Destination Block

There's no need to connect anything to Outport B due to the fact that the Shared Memory is being written