## WARP: Hardware

Charles Camp

WARP Workshop Rice University October 19, 2006

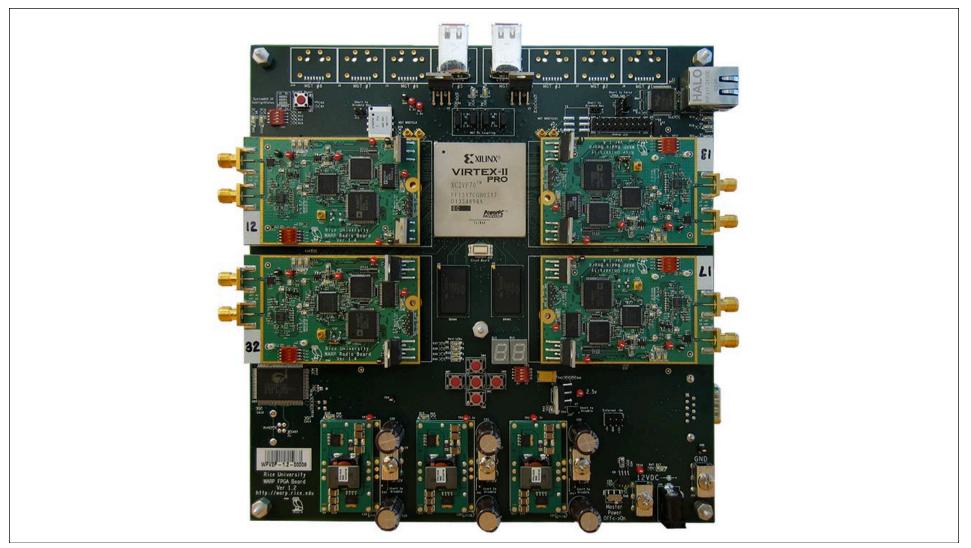

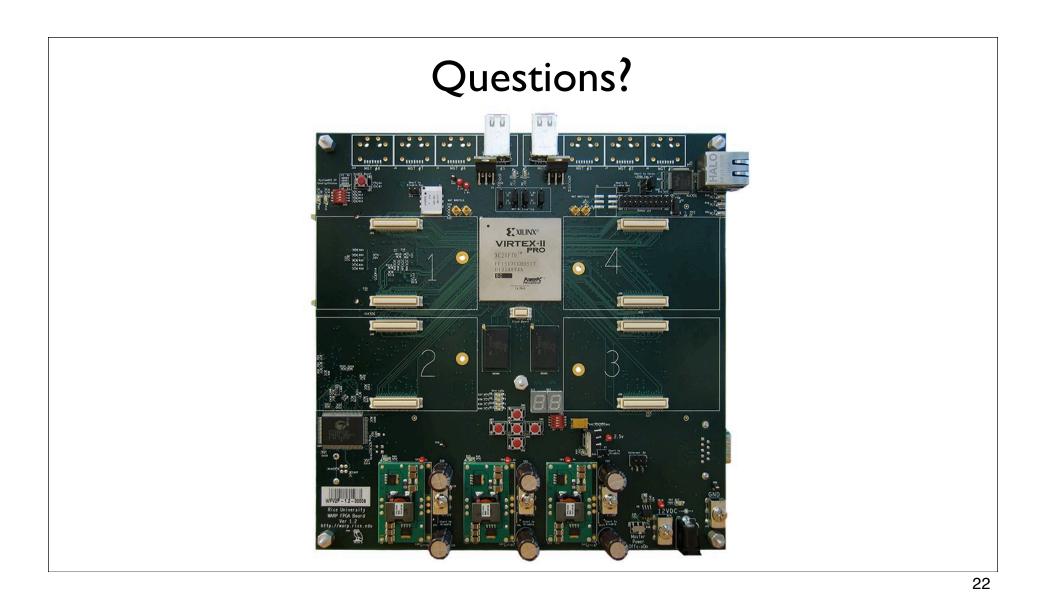

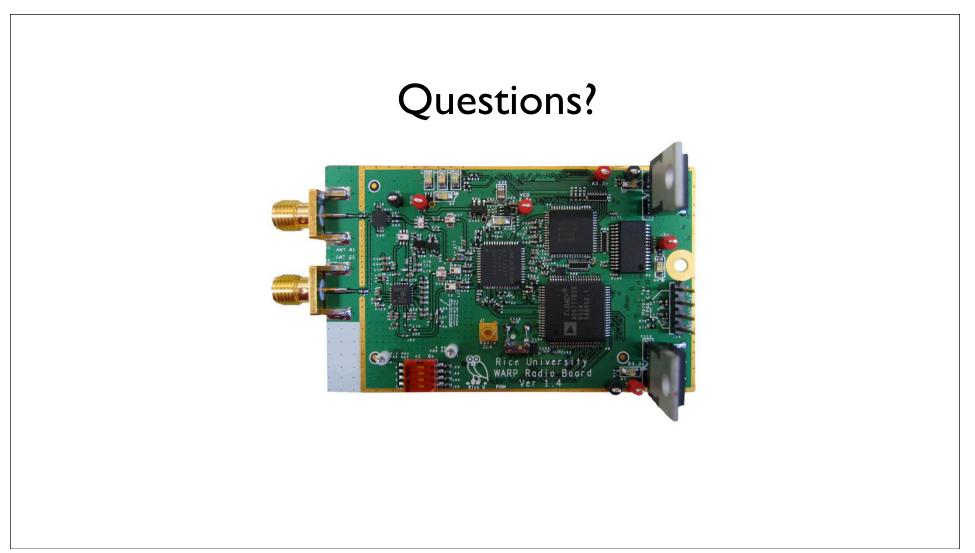

## WARP Hardware

- WARP Hardware Components

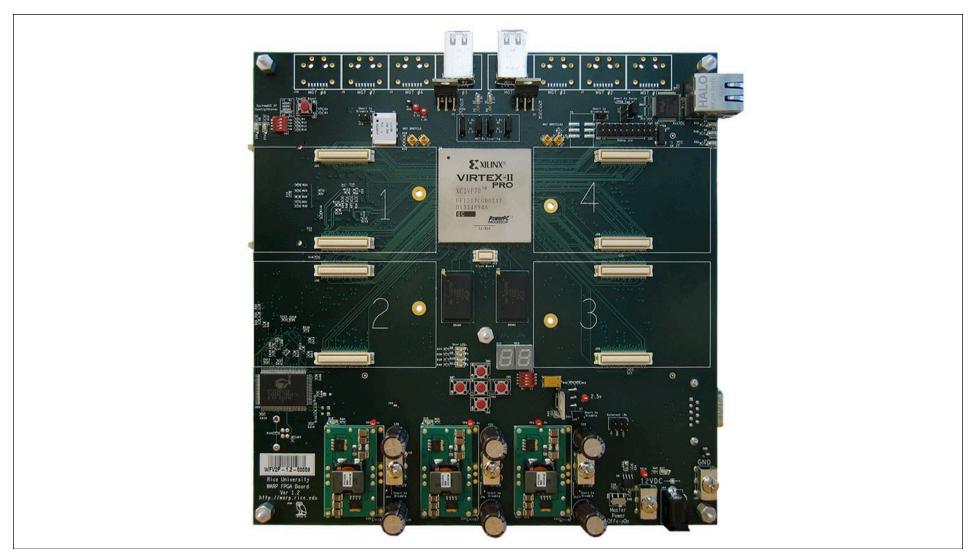

- FPGA Board

- Radio Board

- FPGA Architecture

- Targeting WARP Hardware

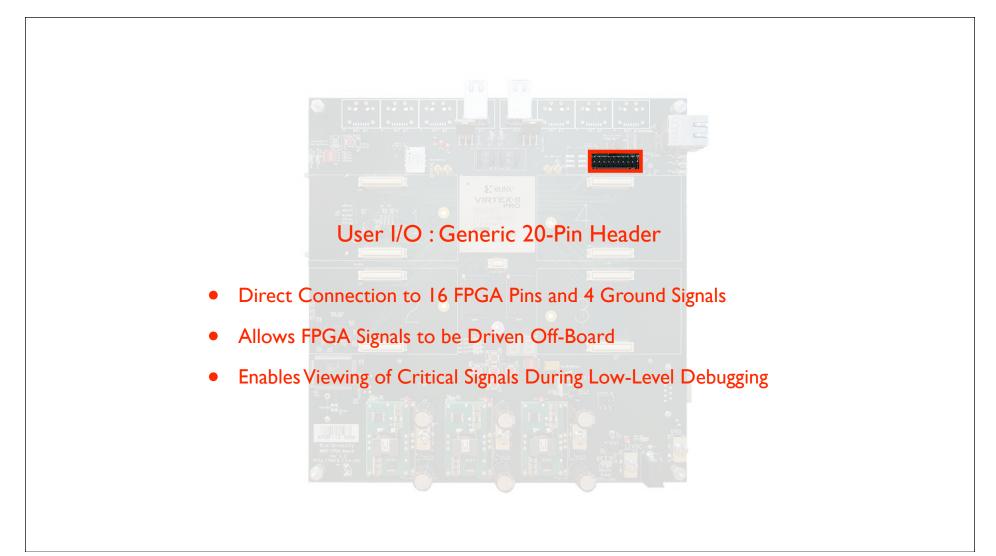

- Provide Expanded Functionality via Custom Daughtercards

- Connect to FPGA Through General Purpose Digital I/Os

- Protocol Defined By Logic and Software Residing in FPGA

- Supports Radios, Video Cards, A/D & D/A Cards, Others

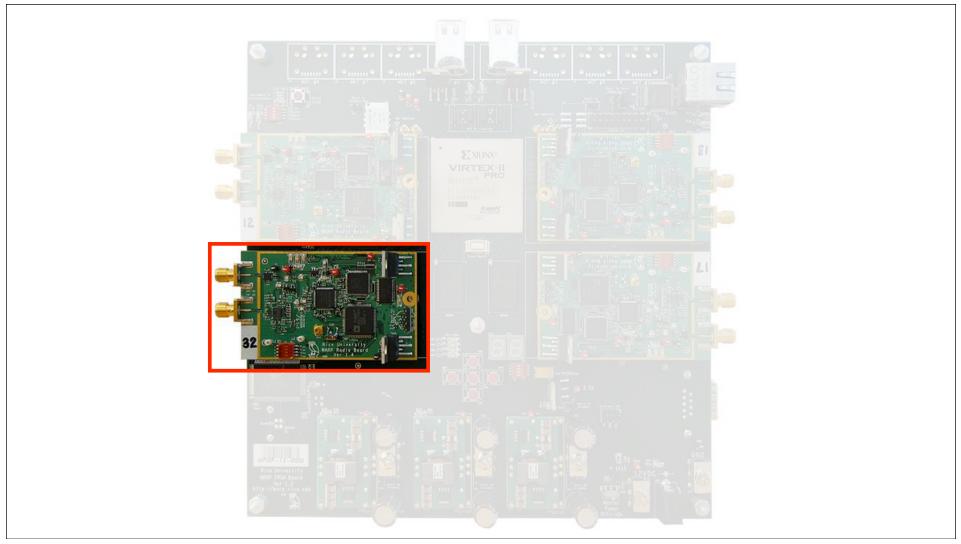

## WARP Hardware

- WARP Hardware Components

- FPGA Board

- Radio Board

- FPGA Architecture

- Targeting WARP Hardware

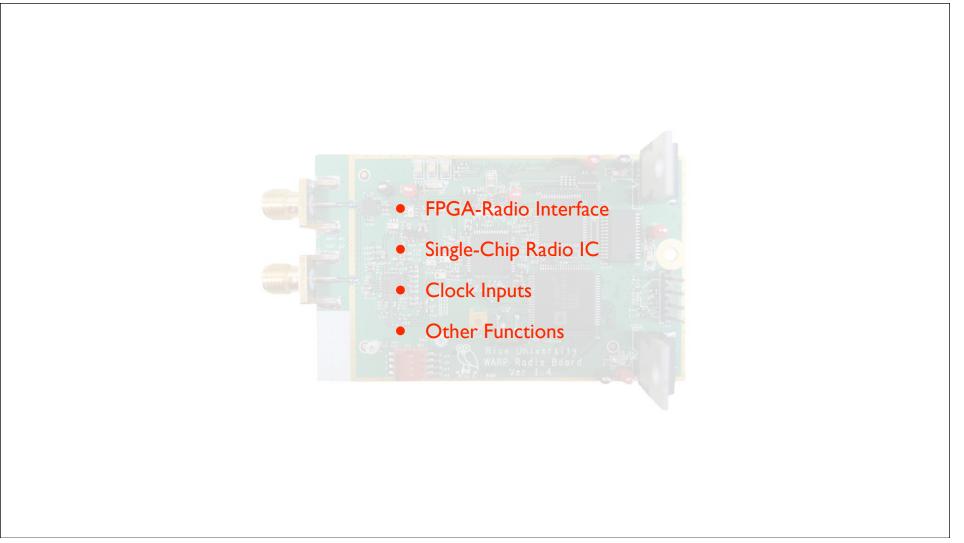

## FPGA-Radio Interface : RSSI A/D Converter

- 10-Bit Representation of Radio Chip's Rx Signal Strength

- Values Used for Packet Detection in Physical Layer

# WARP Hardware

- WARP Hardware Components

- FPGA Board

- Radio Board

- FPGA Architecture

- Targeting WARP Hardware

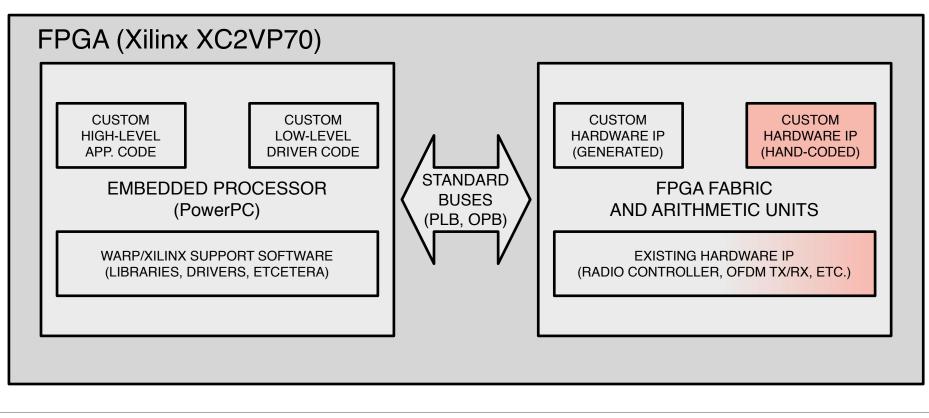

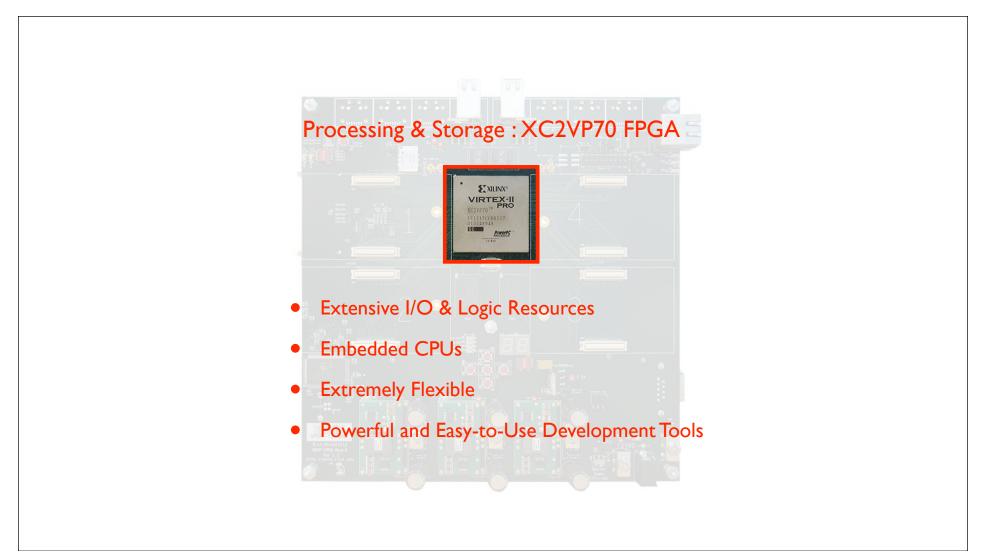

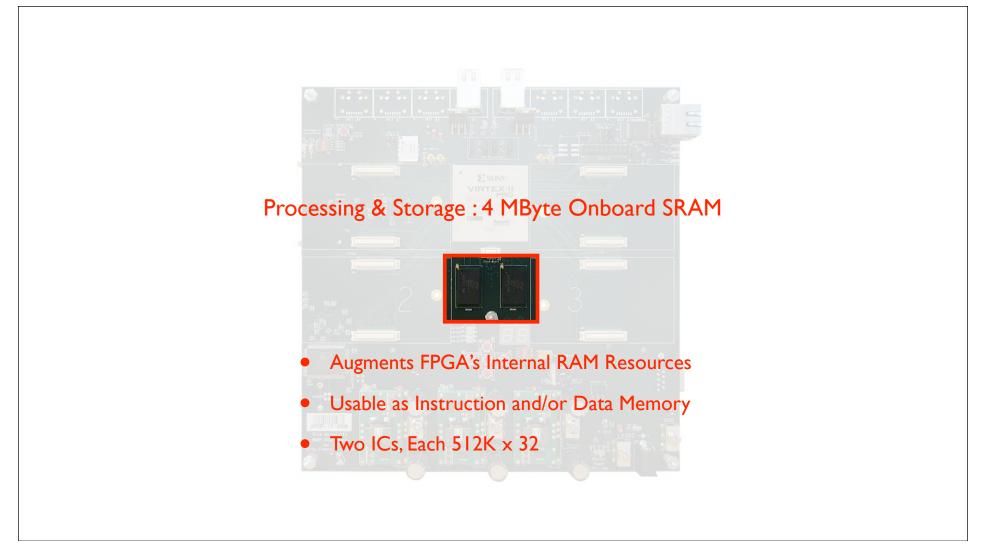

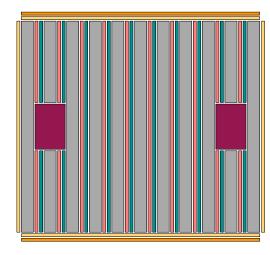

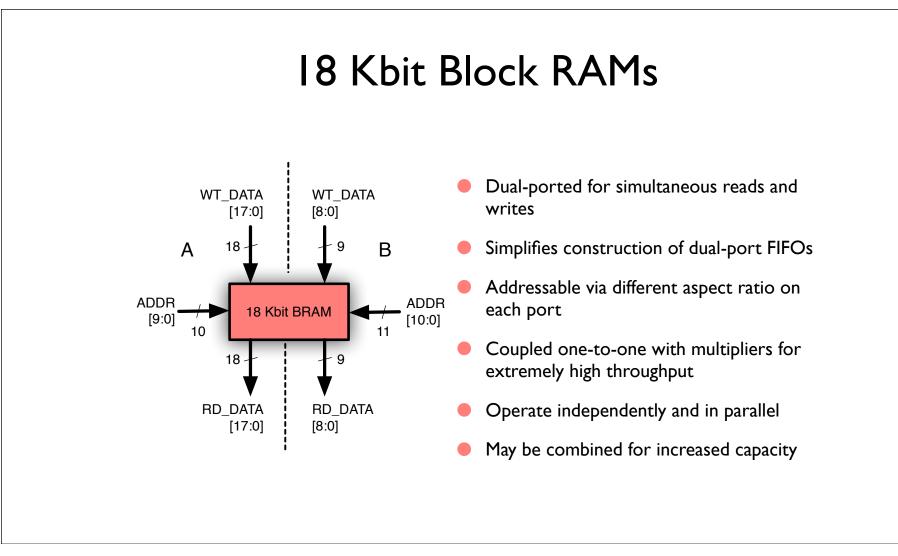

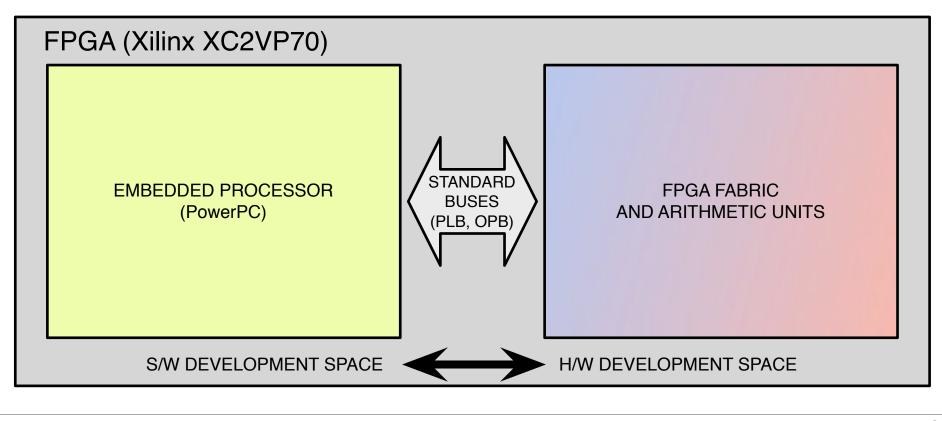

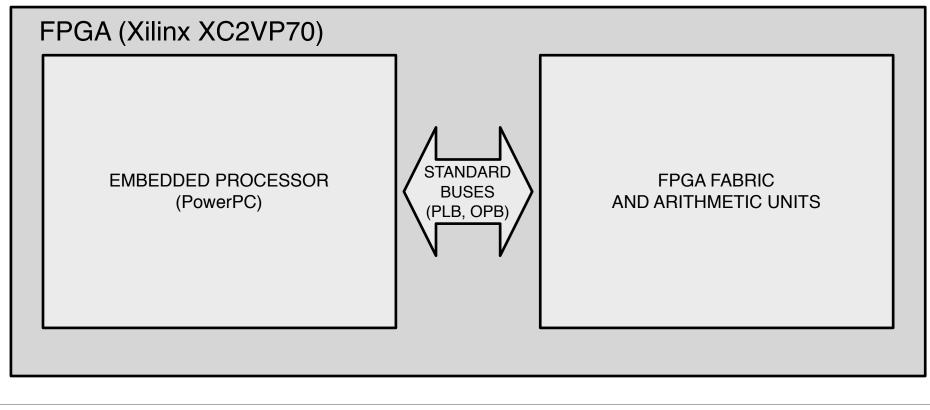

## XC2VP70 Resources

- Embedded PowerPC processors

- 18-Bit by 18-Bit multipliers

- I8 Kbit block RAMs

- General purpose I/Os

- Multi-gigabit transceivers (MGTs)

- Reconfigurable user logic (Fabric)

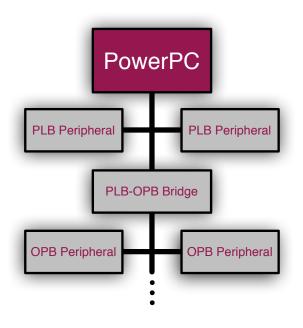

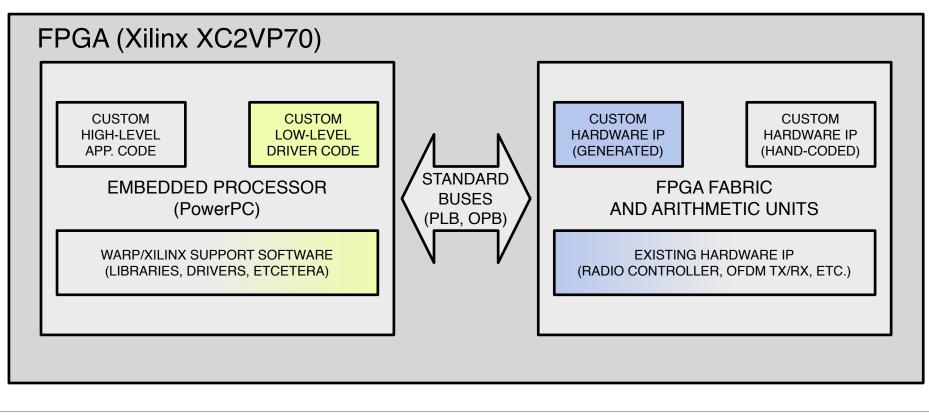

- PPCs connect to peripherals through the IBM Processor Local Bus (PLB)

- Alternative connections via the simpler On-Chip Peripheral Bus (OPB)

- PPCs execute user software for high-level control and data processing

- WARP tools simplify implementation of custom OPB-compliant peripheral cores

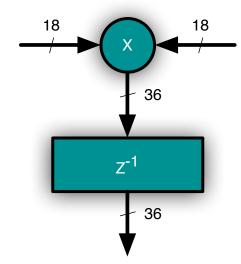

## 18-Bit x 18-Bit Multipliers

- Signed fixed-point inputs and outputs

- Fully synchronous operation with one result per clock cycle

- Tightly coupled with embedded block

RAMs for very high throughput

- Operate independently and in parallel

- May be combined to support larger operands and results

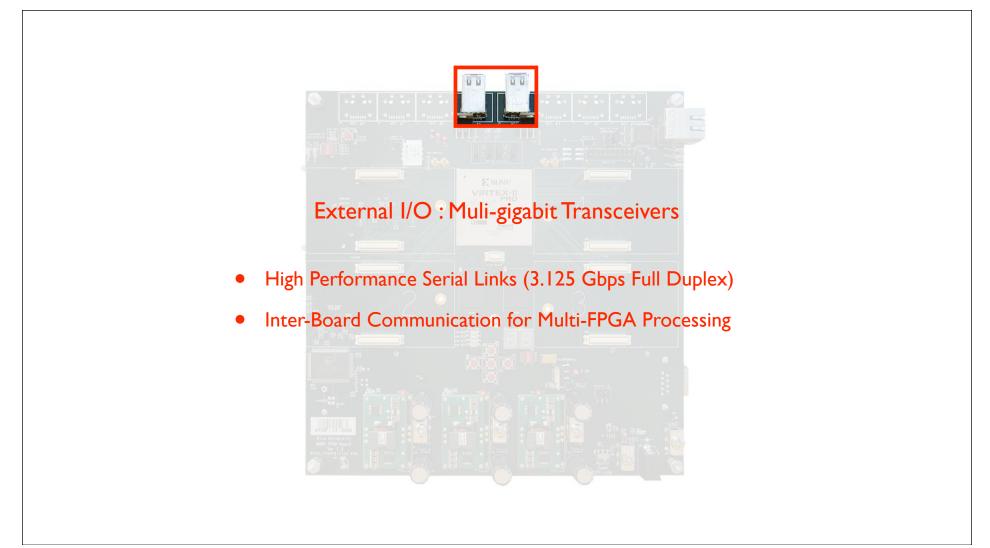

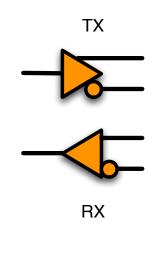

## Multi-Gbit Transceivers

- High-speed serial links : 622 Mbps up to 3.125 Gbps

- Implement Physical Media Attachment and Physical Coding sublayers

- Perform 8b/10b encoding and decoding

- Clock and data recovered from received data stream

- Usable in low latency mode when clocks are matched at Tx and Rx

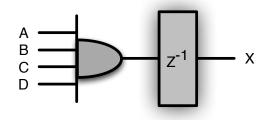

### User Logic (FPGA Fabric)

- Fine-grained array of reconfigurable logic based on 4-input LUTs

- Distributed throughout device

- Interspersed with discrete flip-flops for efficient implementation of registered logic

- Implements general purpose user functionality (e.g. WARP OFDM transceivers)

- Glues together and enhances dedicated cores within the FPGA

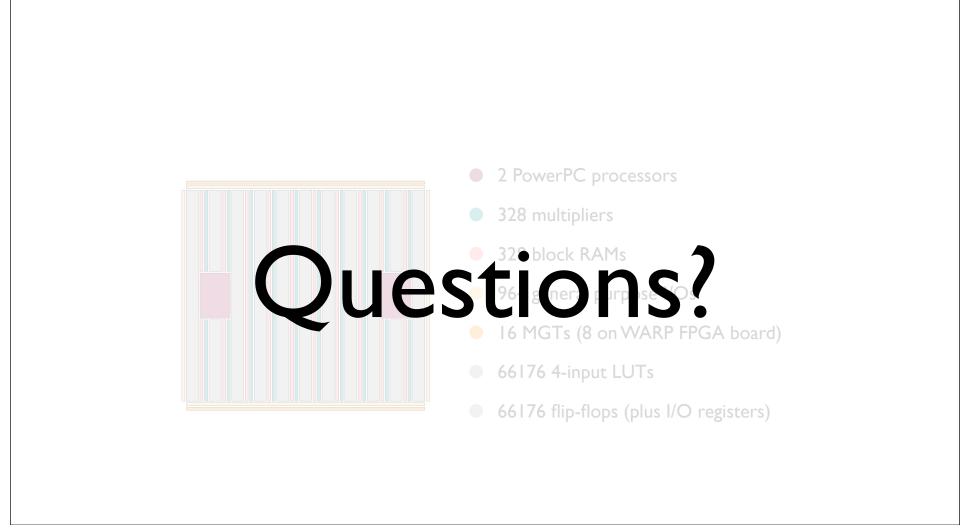

# XC2VP70 Resources

- 2 PowerPC processors

- 328 multipliers

- 328 block RAMs

- **964** general purpose I/Os

- I6 MGTs (8 on WARP FPGA board)

- 66176 4-input LUTs

- 66176 flip-flops (plus I/O registers)

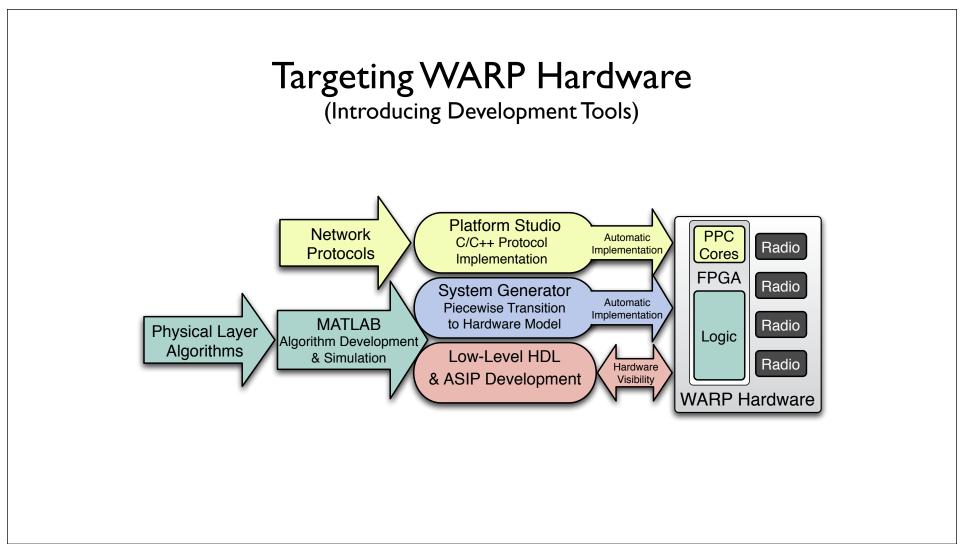

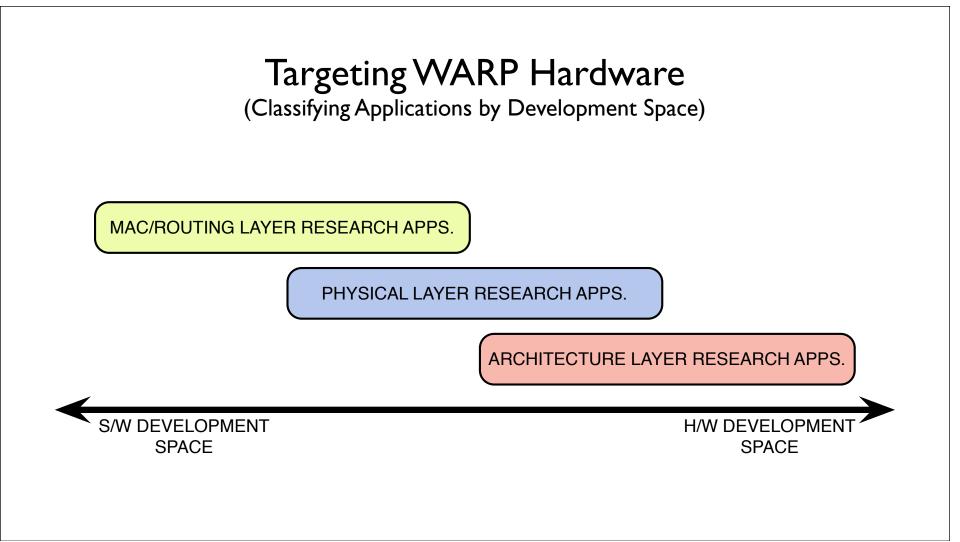

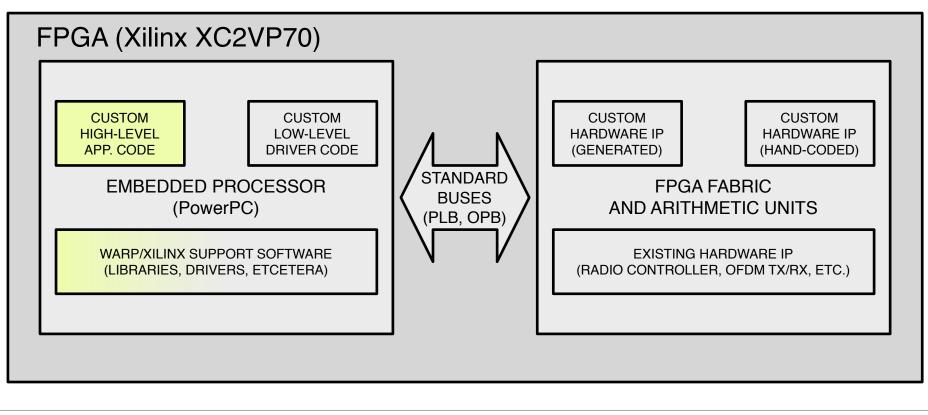

# WARP Hardware

- WARP Hardware Components

- FPGA Board

- Radio Board

- FPGA Architecture

- Targeting WARP Hardware

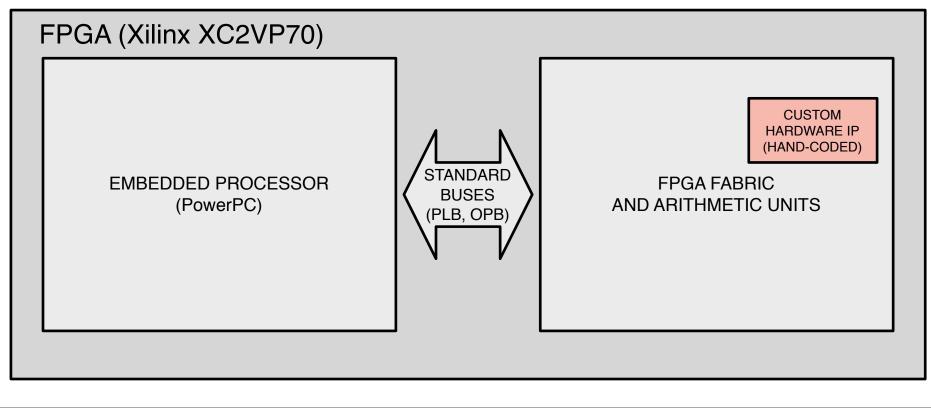

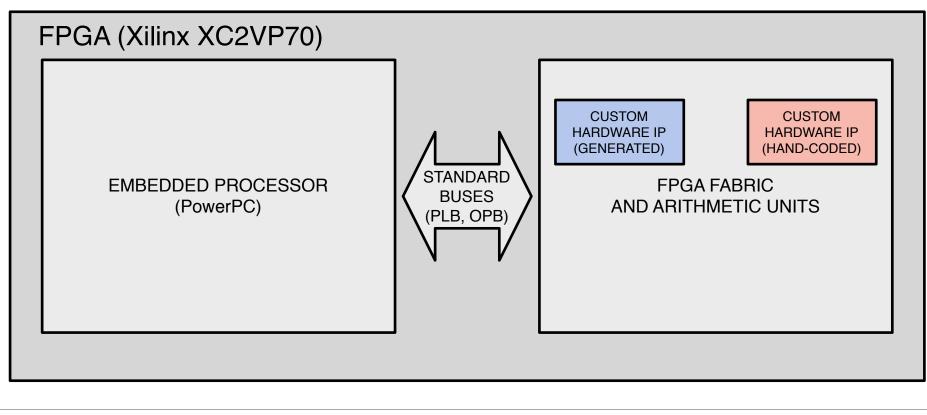

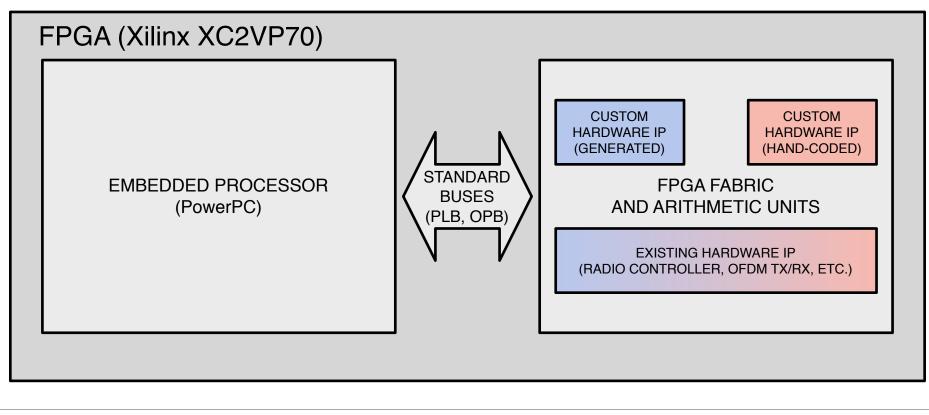

- Hardware Development Efforts

- Hand-Coding Hardware Designs (Verilog, VHDL)

- Generating Hardware Designs (System Generator)

- Interfacing with Existing Hardware IP

- Software Development Efforts

- Low-Level Driver Development

- High-Level Application Development

- Interfacing with Existing Software

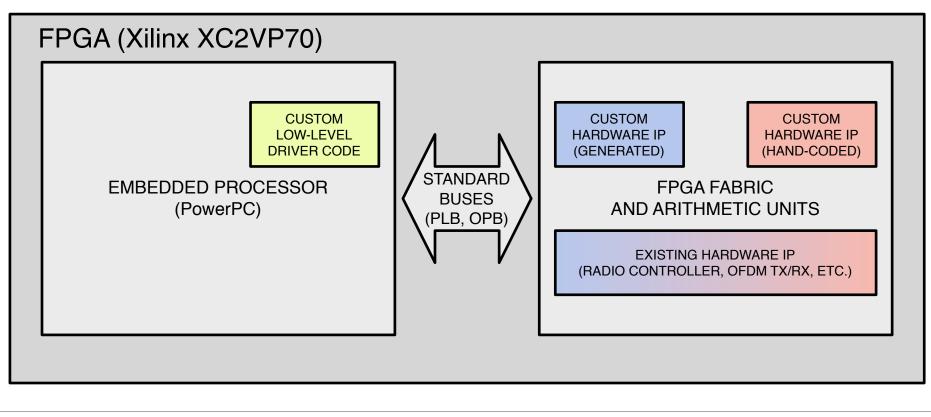

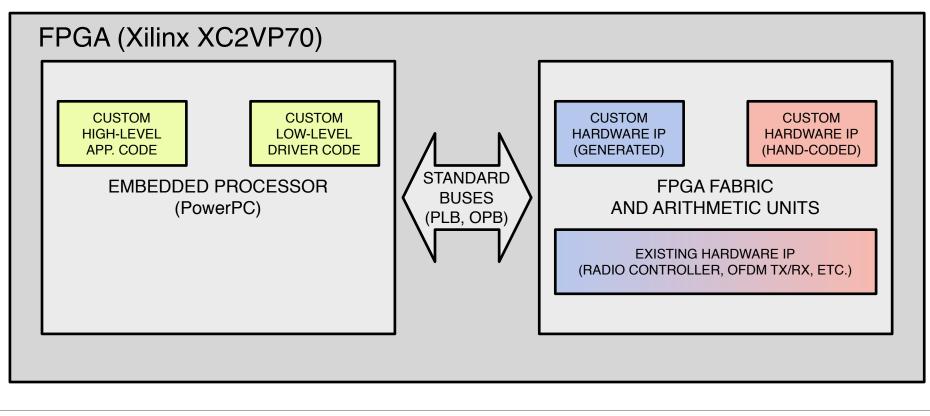

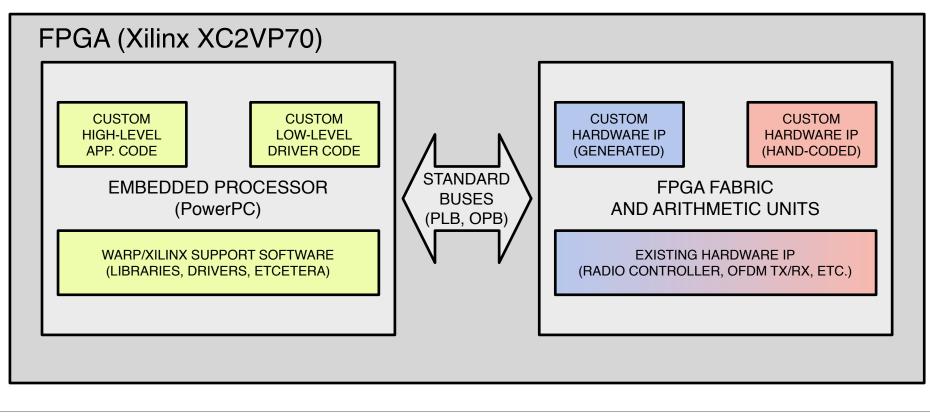

(Classifying FPGA Resources by Development Space)

(MAC/Routing Layer Development Space)

(Physical Layer Development Space)

(Architecture Layer Development Space)