WARP v3 Getting Started Exercises

Developing custom applications on WARP requires using design tools from Xilinx. These tools are sophisticated (i.e. they're complicated) and can be daunting to a new user. We've created some simple exercises that introduce the core tools most WARP users will use.

Basic Design Structure

All WARP reference designs are built using the Xilinx Embedded Development Kit (EDK). The EDK enables construction of designs with both a processor, for running custom software, and custom hardware cores for real-time processing and connecting to off-chip hardware.

The EDK includes two primary tools:

- Xilinx Platform Studio (XPS): integrates the hardware cores for a design, including the MicroBlaze processor, memory, peripherals and interfaces for off-chip hardware

- Xilinx Software Development Kit (SDK): a full suite of software compilation and debugging tools for the MicroBlaze processor

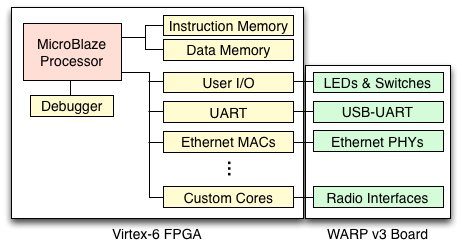

The basic structure of WARP reference designs is illustrated below.

The major components of this architecture are:

- MicroBlaze soft processor: The MicroBlaze is a processor core implemented in the FPGA fabric and is supplied by Xilinx as part of the EDK. This processor replaces the hard PPC405 core familiar to users of WARP v1 and v2.

- Memories: the Virtex-6 FPGA includes a large number of "block RAMs", or internal RAM blocks which can be interconnected to form arbitrarily sized memory areas accessible to the MicroBlaze. These block RAMs are used for cache, instruction and data storage.

- Processor bus: a standard bus connects the MicroBlaze to each core in the system. Current reference designs use a bus called PLB; future designs will migrate to the newer AXI standard.

- Peripheral cores: a collection of peripheral cores compose every hardware design. Some are provided by Xilinx (like the UART and Ethernet MAC). We have designed others (like the WARP v3 user I/O and radio interface cores).

- Off-chip resources: these blocks represent the other hardware on WARP v3 besides the FPGA, like the radio interfaces, FTDI USB-UART transceiver and Marvell Ethernet PHYs

The MicroBlaze processor and connected cores are all implemented in the FPGA fabric using XPS. The output of the XPS flow is a "bitstream" with the fully synthesized and implemented hardware design. This bitstream integrates the MicroBlaze, the standard peripheral cores, your custom cores, I/O assignments and clock configurations. However the MicroBlaze instruction and data memories are blank in this bitstream.

The XPS-generated bitstream (and its associated hardware specification) is the starting point for an SDK project. The SDK compiles custom code for the MicroBlaze, along with drivers for the various cores included in the XPS hardware design. The output of this process is an "elf" file, the software binary ready for execution by the MicroBlaze. The elf binary is combined with the XPS-generated bitstream to program the FPGA with the final hardware+software design.

Exercises

We have designed the exercises below to introduce the Xilinx tools we use for building designs on WARP v3. We recommend working through the exercises in order.

Introduction to the Software Development Kit: This is the classic "hello world" project for WARP v3 using the Xilinx SDK. This exercise shows:

- How to create a Xilinx SDK workspace and import existing hardware, bsp and software projects

- How to update C code and compile the software project

- How to download and execute a software project on WARP v3

Introduction to Xilinx Platform Studio: This exercise introduces Xilinx Platform Studio (XPS). This exercise shows:

- How to open and navigate one of the WARP v3 template projects

- How to instantiate a custom peripheral core in XPS

- How to access the custom core's registers from a software project in the SDK

Exporting a Peripheral Core from System Generator: In this exercise, you will create a custom peripheral using Xilinx System Generator (an FPGA design tool integrated with MATLAB/Simulink). This custom peripheral can then be used in an XPS project, using the procedure introduced in the XPS Intro exercise above.

Reference Designs

Once you're comfortable with the design flows introduced by the exercises above, we recommend getting started with one of our reference designs.

- WARPLab: A framework for rapid prototyping of physical layer algorithms in MATLAB, using real signals transmitted/received via WARP hardware.

- OFDM Reference Design: Implements an OFDM physical layer transceiver and CSMA MAC protocol, both of which operate in real-time in the FPGA