| Version 3 (modified by murphpo, 15 years ago) (diff) |

|---|

Custom User I/O Control Core

A custom core for user I/O control is available in the repository and during the base system builder process. The core allows the user to control the LEDs, read the push buttons and DIP switches and output patterns to the 7-segment displays. The core also implements the mapping of 4-bit hexadecimal characters to 7-bit patterns used to drive the 7-segment displays. This mapping is enabled per display at runtime by user designs.

Register Bank

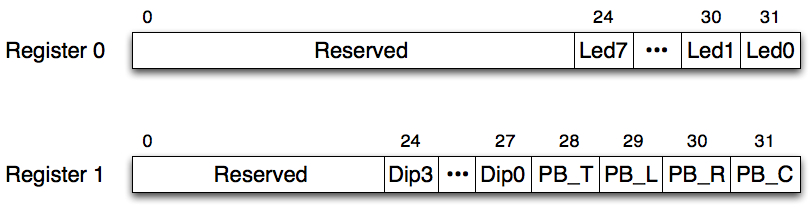

The core has 5 registers that enable the I/O functionality. Register 0 and 1 are the output and input registers for the dedicated I/O, namely the LEDs, the push buttons and the DIP switch.