802.11 Reference Design: Architecture

The 802.11 Reference Design is implemented entirely in the FPGA of the WARP v3 node. PHY processing is divided across multiple cores (Tx, Rx, AGC, hardware control, etc.). The MAC is implemented primarily in software running in two MicroBlaze CPUs, with a support core in the FPGA to achieve accurate inter-packet timing. The overall design is integrated in Xilinx Platform Studio (XPS). The source code/models for all components are available in the repository (/ReferenceDesigns/w3_802.11) and are distributed under the Mango Reference Design License.

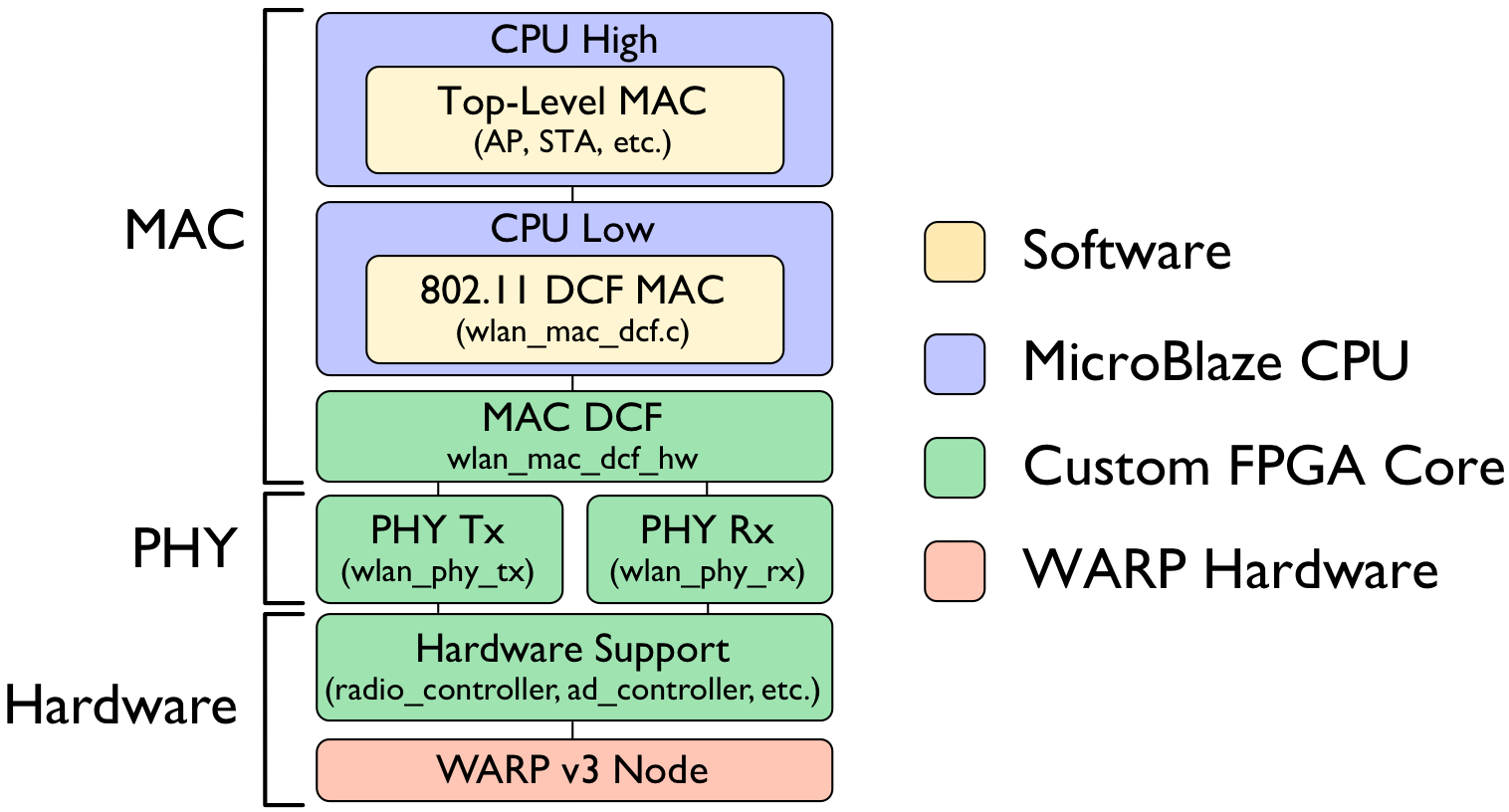

The overall architecture of the design is illustrated below.

802.11 FPGA Cores

- CPU High: MicroBlaze CPU executing the top-level MAC code and other high-level functions. The code in CPU High is responsible for constructing all non-control packets for transmission and for implementing the various handshakes with nodes (probe request/response, association request/response, etc.). CPU High is also responsible for integrating with a wired network, implementing encapsulation and de-encapsulation of Ethernet frames according to the wired-wireless integration described in Annex P of the IEEE 802.11-2012 standard. CPU High is clocked at 160MHz.

- CPU Low: MicroBlaze CPU executing low-level code for the MAC distributed coordination function (DCF). This code is responsible for all MAC-PHY interactions and for handling intra-packet state that is time critical. This includes transmission of ACKs, scheduling of backoffs, maintaining the contention window and initiating re-transmissions. The wlan_mac_dcf software project is an implementation of Section 9.3.1 of the 802.11-2012 standard. CPU Low is clocked at 160MHz.

- MAC DCF Core (wlan_mac_dcf_hw): an FPGA core implemented in System Generator which acts as the interface between the MAC software design and the Tx/Rx PHY cores. This core implements the timers required for the DCF (timeout, backoff, DIFS, SIFS, etc.) and the various carrier sensing mechanisms. The MAC DCF core monitors the Tx and Rx PHY cores and sequences Tx and Rx events per the configuration provided by the MAC software.

- PHY Tx/Rx: These peripheral cores implement the OFDM physical layer transceiver specified in Section 18 of the 802.11-2012 standard. Details are available in the PHY page. The PHY cores are clocked at 160MHz (8x the I/Q sample rate).

- Hardware Support: These cores are drawn from the standard platform support cores for WARP v3 (w3_ad_controller, radio_controller, etc.) and enable control of the various peripheral interfaces on WARP v3 from the code in CPU Low.

Design Integration

The 802.11 Reference Design is implemented as a Xilinx Platform Studio project. The XPS project integrates the CPUs, PHY cores, MAC core, hardware support cores and FPGA pin and timing constraints. The output of the XPS project is a fully-implemented FPGA design ready for use in the Xilinx SDK. The MAC code is compiled in the SDK and added to the FPGA design. The combined hardware+software design is used to configure the WARP v3 FPGA.

If you are not familiar with the System Generator -> XPS -> SDK -> hardware design flow, please review our tutorials. These tutorials introduce the same design tools used for the 802.11 Reference Design using a much simpler example design.