WARP FPGA Board Ethernet

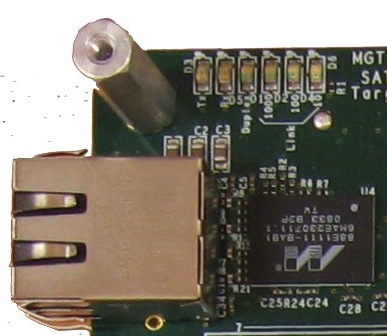

The FPGA Board has one 10/100/1000 Ethernet device present. The design uses the Marvell 88e1111 Gigabit Ethernet PHY. The Marvell PHY implements all the physical layer functionality and the Virtex-4 FPGA uses one of the hardened Tri-mode Ethernet MAC for the MAC layer. Any MAC layer implementation in the Virtex-4 utilizes the hard TEMAC and the soft LocalLink TEMAC.

There are six status LEDs (D1 - D6) which show the status of the physical layer link.

| Label | LED Color | Status |

| Tx | Green | Lights up during packet transmission |

| Rx | Green | Lights up during packet reception |

| Duplex | Red | Indicates the successful negotiation of a duplex link |

| 10 | Red | Indicates negotiated speed of 10 Mbps |

| 100 | Red | Indicates negotiated speed of 100 Mbps |

| 1000 | Red | Indicates negotiated speed of 1 Gbps |

The auto-negotiated speeds are between the physical layers of the two Ethernet devices. The Ethernet MAC must still be informed of the correct speed to use or the auto-negotiation callback must be implemented.

FPGA Constraints

# FPGA Board v2.2 constraints for gigabit Ethernet # # The Ethernet connector (J15) is located on the left side # Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<0> LOC = D17 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<1> LOC = E17 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<2> LOC = K17 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<3> LOC = G15 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<4> LOC = J16 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<5> LOC = J17 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<6> LOC = H17 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TXD_0_pin<7> LOC = K16 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TX_EN_0_pin LOC = C18 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TX_ER_0_pin LOC = K18 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_TX_CLK_0_pin LOC = F21 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<0> LOC = K23 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<1> LOC = E21 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<2> LOC = E22 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<3> LOC = H22 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<4> LOC = J24 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<5> LOC = G23 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<6> LOC = E23 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RXD_0_pin<7> LOC = G21 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RX_DV_0_pin LOC = H23 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RX_ER_0_pin LOC = F23 | IOBDELAY = NONE | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_GMII_RX_CLK_0_pin LOC = J22 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_MII_TX_CLK_0_pin LOC = G22 | PERIOD = 40 ns | MAXSKEW= 1.0 ns | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_MDIO_0_pin LOC = L16 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_MDC_0_pin LOC = H15 | IOSTANDARD = LVCMOS25; Net fpga_0_TriMode_MAC_GMII_TemacPhy_RST_n_pin LOC = C17 | IOSTANDARD = LVCMOS25 | TIG;