| Version 31 (modified by murphpo, 12 years ago) (diff) |

|---|

WARP v3 User Guide: Template Projects

The following template projects demonstrate how to use the various peripherals on the WARP v3 board and are good starting points for your custom designs.

The projects are grouped by the version of Xilinx ISE used. We will update this page as we port the template projects to newer releases of ISE.

Choosing a Project

The On Board Peripherals Template Project contains the full suite of hardware components offered by a standalone WARP v3 board. The Lite version has the same basic architecture, but omits the SDRAM controller and Ethernet MACs. As a result, the Lite project will build faster.

For reference, on a PC with a 3.4GHz i7-2600 processor, 16GB of RAM and running Windows 7 64-bit, build times of the template projects are:

| Project | Build Time |

|---|---|

| On Board Periphs | 17 minutes |

| Lite | 9 minutes |

Note: These times are from projects that had hardware "cleaned" such that no cached support files were used. When iterating on a design, build times will be faster as XPS re-uses cached netlists for unmodified cores.

Xilinx ISE 13.4

On Board Peripherals Template Project

This is an XPS/SDK project which implements peripheral cores to interface with every peripheral on the WARP v3 board, including:

- MicroBlaze soft processor (big-endian, PLB-based design)

- Block RAM for instruction/data memory

- User I/O (LEDs, buttons, UART)

- Dual Ethernet interfaces

- MPMC for DDR3 SO-DIMM access

- Peripherals for RF interface control

- Timer peripheral for user code

Version information:

| Project Version | ISE Version | Bus Arch | EDK Project Download |

|---|---|---|---|

| 1.1 | 13.4 | PLB | w3_TemplateProject_OnBoardPeriphs_v1p1.zip |

We recommend downloading the latest version of this project that matches the version of the ISE tools you have installed.

Release Notes:

- v1.1 (Nov 2012)

- Swapped LSB/MSB for DIP switch, so LSB is right-most switch

- Updated Ethernet constraints for ETH_A MDIO signals

- v1.0 (Aug 2012)

- Initial release of template project

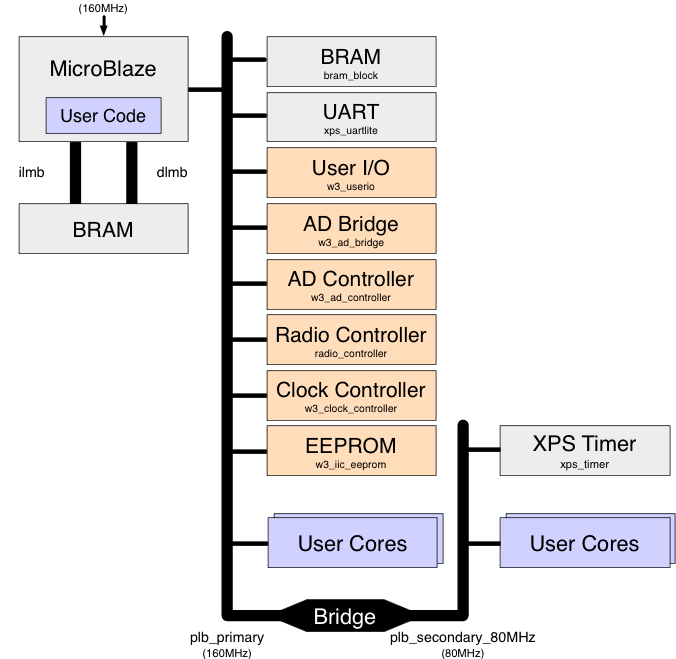

Lite Project

This is an XPS/SDK project which implements a subset of the peripheral cores from the full project above, including.

- MicroBlaze soft processor (big-endian, PLB-based design)

- Block RAM for instruction/data memory

- User I/O (LEDs, buttons, UART)

- Peripherals for RF interface control

- Timer peripheral for user code

If your application requires use of the DDR3 SO-DIMM or Ethernet, you should use the On Board Peripherals project instead.

Version information:

| Project Version | ISE Version | Bus Arch | EDK Project Download |

|---|---|---|---|

| 1.1 | 13.4 | PLB | w3_TemplateProject_Lite_v1p1.zip |

We recommend downloading the latest version of this project that matches the version of the ISE tools you have installed.

- v1.1 (Nov 2012)

- Swapped LSB/MSB for DIP switch, so LSB is right-most switch

- Updated Ethernet constraints for ETH_A MDIO signals

- v1.0 (Aug 2012)

- Initial release of template project

Other Projects

The XPS/SDK projects for the latest OFDM Reference Design and WARPLab Reference Design are also available. Both of these reference projects are based on the On Board Peripherals template above.

Attachments (4)

- lite.pdf (18.6 KB) - added by chunter 12 years ago.

- onboardperiph.pdf (19.2 KB) - added by chunter 12 years ago.

- onboardperiph.png (76.1 KB) - added by chunter 12 years ago.

- lite.png (63.3 KB) - added by chunter 12 years ago.

Download all attachments as: .zip