WARP v3 User Guide: RF Interfaces

The WARP v3 board integrates two identical RF interfaces. The basic structure of each interface is illustrated below.

On the WARP v3 board and in our reference designs, these interfaces are labeled RF A and RF B, where RF A is nearer the top edge of the board (closer to the hex displays).

AD9963 ADC/DAC

The conversion between the analog I/Q and digital I/Q domains is handled by the Analog Devices AD9963 MxFE. The AD9963 integrates two 100MSps 12-bit ADCs, two 170MSps 12-bit DACs, interpolation and decimation filters and programmable analog gain and offset adjustments. Refer to the ADI AD9963 datasheet for full specifications.

The AD9963 is very flexible and includes a register bank to control various functions on the chip. The registers are accessed via a dedicated SPI interface. We have designed the w3_ad_controller core to access the AD9963 registers via the SPI interface.

The digital I/Q ports on the AD9963 operate at double data rate, with I/Q interleaved. We have designed the w3_ad_bridge core to connect these DDR ports to separate internal I/Q busses in user designs.

Tx Data Path

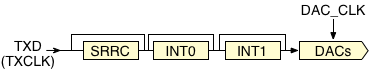

The AD9963 integrates 3 stages of digital interpolation filters. These filters can be en/disabled at run time via SPI register writes. By cascading the filters the AD9963 can apply interpolation of 1x, 2x, 4x or 8x.

A single AD9963 Tx data path is illustrated below. Identical data paths are implemented for both DACs (I and Q).

| Int Rate | Enabled Filters |

|---|---|

| 1 | None |

| 2 | INT0 |

| 4 | INT0, INT1 |

| 8 | INT0, INT1, SRRC |

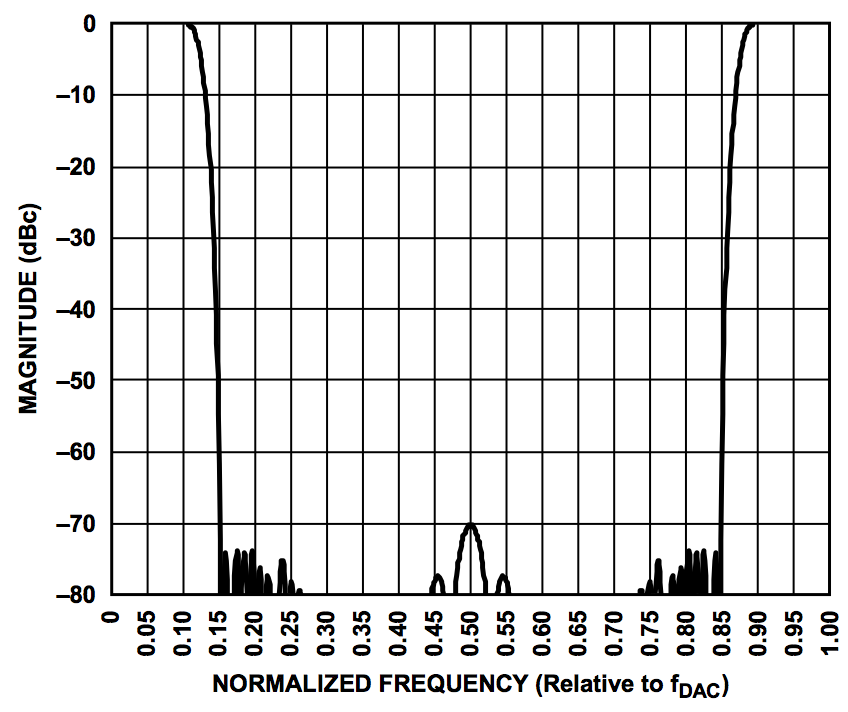

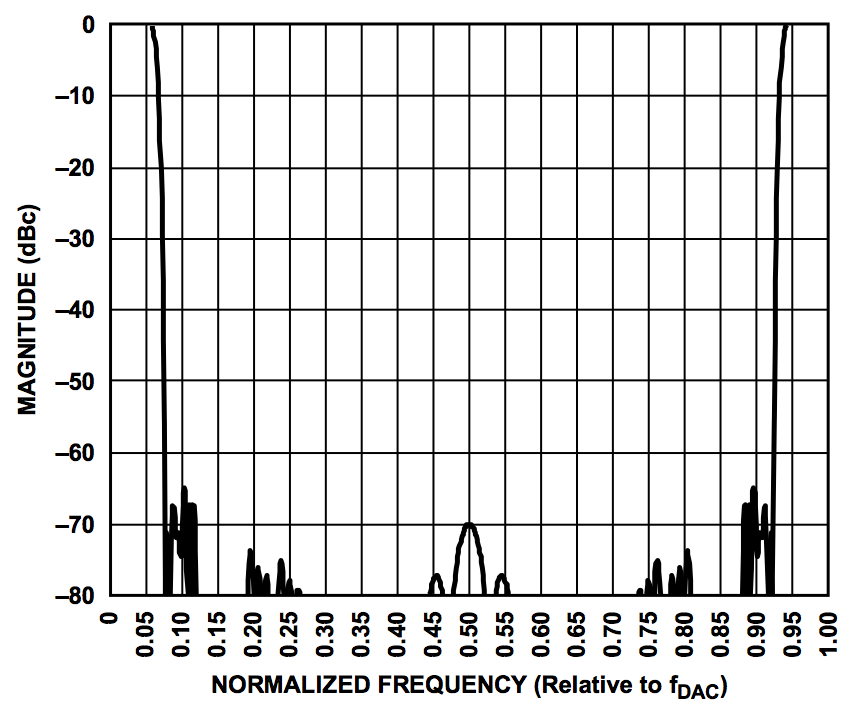

The figures below show the effective frequency response of the Tx path for interpolation rates 2, 4, and 8. The frequency axis is normalized to the DAC sampling rate. Click each figure for the full-resolution. These figures come from pg. 38 of the AD9963 datasheet.

| 2x Interpolation | 4x Interpolation | 8x Interpolation |

|---|---|---|

|  |

|

Refer to the AD9963 datasheet for the coefficients used in each interpolation filter.

Note that when the interpolation filters are enabled, the user-supplied Tx I/Q samples and the DAC sampling clock run at different frequencies. The user design must ensure the data clock (TXCLK) frequency, DAC clock frequency and interpolation filter settings are in agreement.

Rx Data Path

The AD9963 integrates a digital 2x decimation filter. This filter can be en/disabled at run time via an SPI register write. A single Rx data path is illustrated below. Identical data paths are implemented for both ADCs (I and Q).

The effective frequency response when the decimation filter is enabled is shown below. This figure comes from pg. 37 of the AD9963 datasheet. Refer to the datasheet for the actual coefficients used in the decimation filter.

| 2x Decimation |

|---|

|

Note that when the decimation filter is enabled, the Rx I/Q samples and TRXCLK signal will run at a different rate than the ADC sampling clock. The user design must ensure the FPGA clock design and AD9963 filter/clock settings are in agreement.

Clocking

The clocking configuration of the AD9963 is flexible and, as a result, complicated. There are two main clock domains in the AD9963: data clocks, connected to the FPGA, and converter clocks, used by the ADC/DAC cores.

The converter clocks are illustrated below.

Notice that the DAC and ADC clocks are always derived from the AD9963 reference clock input, not the data clock inputs. The data clocks must be synchronous to the converter clocks, but by separating these domains preserves the low jitter of the original reference clock.

The DLL parameters (M/N), ADC clock divider and mux selects are all configured via SPI register writes. The correct settings depend on the desired sampling rate, the Tx and Rx data rates at the FPGA and the AD9963 rate-change filter settings.

The REF_CLK signal is generated by the sampling clock buffer on the WARP v3 board. This signal is derived from the 80MHz TCXO and can be divided by the clock buffer before being driven to the AD9963s. Refer to the WARP v3 Clocking page for more details.

Some examples of valid combinations of clock sources, clock frequencies and filter settings are listed below. Many other valid combinations are possible. Note that the w3_ad_bridge and w3_ad_controller do not enforce valid combinations, as these cores do not know what clocks are connected in hardware. The user design must ensure correct settings.

Example 1

| Example 2

|

Example 3

| Example 4

|

MAX2829 Transceiver

The WARP v3 RF interfaces use the Maxim MAX2829 transceiver to translate between baseband and RF. The MAX2829 implements both 2.4 and 5GHz Tx/Rx paths. For full specifications refer to the MAX2829 datasheet.

The MAX2829 transceiver has a number of digital control lines and a dedicated SPI interface for internal register access. We have designed the radio_controller core to manage these control interfaces in user designs.

Each transceiver generates its own RF carrier signal, derived from a reference clock input. The reference clocks for both RF interfaces are driven by an AD9512 clock buffer (see for details). The MAX2829 requires either a 20MHz or 40MHz reference clock. The AD9512 must be configured to divide its 80MHz input to generate the desired reference frequency.

Power Amplifier

The WARP v3 design currently uses the Anadigics AWL6951 dual-band power amplifier. Every board is tested to ensure >20dBm output power at both 2.4 and 5GHz. Refer to the AWL6951 datasheet for full specifications.

RF Port

Each RF interface is connected to a 50 ohm SMA jack. This connector is a standard polarity, standard thread SMA jack. The SMA jack should always be terminated into a 50 ohm load. The WARP v3 kit includes SMA terminators for each RF interface. Users must supply their own RF cables or antennas to suit their application.

The maximum input power at the SMA connector should never exceed 0dBm, to avoid damage to the MAX2829 RF inputs.

The performance of the MAX2829 RF inputs are specified for input powers below approximately -10dBm. To connect two WARP v3 kits via a coax cable, ensure there is at lest 40dB series attenuation.

Tx DCO Calibration

Each analog Tx I/Q path on WARP v3 may have small DC offset. This is caused by normal variations in component values and inherent offsets in the analog and RF ICs. It is important this DC offset is removed to avoid carrier leakage (LO leakage) in transmitted RF waveforms.

Applying Tx DCO Calibration

Every node is calibrated during manufacturing, with the calibration values stored in the board's EEPROM. You should read and apply these calibration values in every custom design which uses the RF interfaces.

The Tx DCO calibration values are stored at dedicated bytes in the EEPROM. See the EEPROM page for details.

The WARP v3 design uses auxiliary DACs in the AD9963 to apply small DC offsets to the differential I/Q DAC outputs. The auxiliary DACs are configured via SPI. The w3_ad_controller driver provides functions for writing the DAC values from user code.

User designs should read Tx DCO calibration values from the EEPROM and update the AD9963 auxiliary DACs on every boot. The radio_controller driver provides the function radio_controller_apply_TxDCO_calibration() implementing this process.

Updating Tx DCO Calibration

You may wish to occasionally re-run the Tx DCO calibration process to account for drift in component values with temperature and age. We provide a pre-built FPGA design which implements the Tx DCO calibration process. To use the design:

- Terminate the RF interface to be calibrated into a 50 ohm load. The SMA terminators included with the WARP v3 kit are good for this. Alternately you can connect the RF interface to a spectrum analyzer to observe the Tx DCO calibration results.

- Connect a micro USB cable to the USB-UART interface, and connect a terminal emulator to the virtual serial port with baud rate 57600bps

- Download warpv3_txdco_calibration.zip and expand the archive

- Configure the WARP v3 node using warpv3_txdco_calibration.bit via JTAG or warpv3_txdco_calibration.bin with an SD card.

- A menu will be printed to the UART; press 1 or 2 to calibrate RF A or RF B

- The calibration process is automatic and executes in ~20 seconds

- When complete, the new calibration values will be recorded to the EEPROM

- The RF interface will now transmit a pure sinusoid at 2460 MHz (8 MHz baseband tone, center frequency of 2452 MHz). You should observe a very low power tone at the 2452 MHz center frequency, resulting from any residual Tx DCO.

- You can use the keyboard to further adjust the Tx DCO, possibly improving on the auto-calibrated values. If you find values which show less energy at the center frequency, you can re-write the EEPROM by pressing r.

Repeat this process for the other RF interface if desired. Always ensure the SMA connector of the active interface is terminated into a 50 ohm load (50 ohm terminator or other RF sink) before running the calibration routine.