802.11 Reference Design

- Download

- Changelog

- FAQ

- Architecture

Using the Design

Benchmarks

- IFS Calibration

- Throughput

- Transmitter Characterization

- Receiver Characterization

- Pkt. Det. Min. Power Characterization

MAC

Upper-level

Lower-level

- PHY

Experiments Framework

- Packet Flow

- FPGA Architecture

- FPGA Resource Usage

- App Notes

- Other Resources

- License

- Changelog

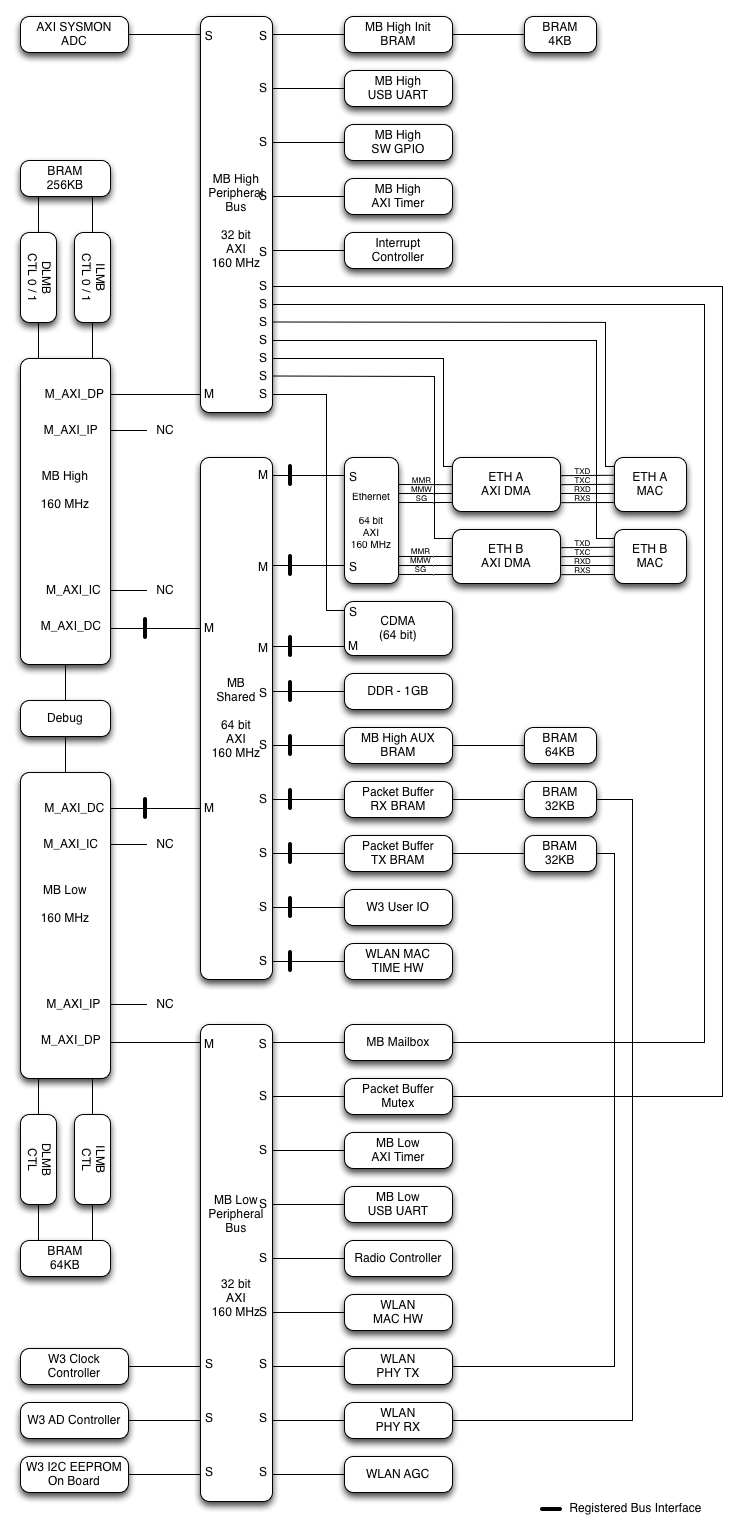

802.11 Reference Design version 1.4.0 FPGA Architecture for WARP v3 Hardware

The 802.11 Reference Design version 1.4.0 for WARP v3 makes changes to the underlying FPGA architecture. This includes:

- New MAC time hardware core

- Updates to Ethernet hardware (makes ETH A and ETH B equivalent)

- Updates to peripheral address map

- See changelog for other updates

Interconnect Architecture

Address Map

Please review the XPS project for the latest information.

CPU High Microblaze Address Map

NOTE: All Address not explicitly defined are reserved.

| IP Instance | Base Address | High Address | Size |

|---|---|---|---|

| DLMB_0 | 0x0000_0000 | 0x0001_FFFF | 128K |

| ILMB_0 | 0x0000_0000 | 0x0001_FFFF | 128K |

| DLMB_1 | 0x0002_0000 | 0x0003_FFFF | 128K |

| ILMB_1 | 0x0002_0000 | 0x0003_FFFF | 128K |

| BRAM (init) | 0x1000_0000 | 0x1000_0FFF | 4K |

| AXI GPIO (software) | 0x2000_0000 | 0x2000_FFFF | 64K |

| USB UART | 0x2100_0000 | 0x2100_FFFF | 64K |

| Interrupt Controller | 0x2200_0000 | 0x2200_FFFF | 64K |

| AXI Timer | 0x2300_0000 | 0x2300_FFFF | 64K |

| AXI SYSMON ADC | 0x2400_0000 | 0x2400_FFFF | 64K |

| Mailbox | 0x3000_0000 | 0x3000_FFFF | 64K |

| Mutex | 0x3100_0000 | 0x3100_FFFF | 64K |

| ETH A MAC | 0x4000_0000 | 0x4003_FFFF | 256K |

| ETH B MAC | 0x4100_0000 | 0x4103_FFFF | 256K |

| AXI DMA (ETH A) | 0x4200_0000 | 0x4200_FFFF | 64K |

| AXI DMA (ETH B) | 0x4300_0000 | 0x4300_FFFF | 64K |

| CDMA | 0x4800_0000 | 0x4800_FFFF | 64K |

| W3 User IO | 0x8000_0000 | 0x8000_0FFF | 4K |

| WLAN MAC Time HW | 0x8100_0000 | 0x8100_0FFF | 4K |

| BRAM (RX pkt buffer) | 0x9000_0000 | 0x9000_7FFF | 32K |

| BRAM (TX pkt buffer) | 0x9100_0000 | 0x9100_7FFF | 32K |

| BRAM (aux) | 0xA000_0000 | 0xA000_FFFF | 64K |

| DDR | 0xC000_0000 | 0xFFFF_FFFF | 1G |

CPU Low Microblaze Address Map

NOTE: All Address not explicitly defined are reserved.

| IP Instance | Base Address | High Address | Size |

|---|---|---|---|

| DLMB | 0x0000_0000 | 0x0000_FFFF | 64K |

| ILMB | 0x0000_0000 | 0x0000_FFFF | 64K |

| USB UART | 0x2000_0000 | 0x2000_FFFF | 64K |

| AXI Timer | 0x2100_0000 | 0x2100_FFFF | 64K |

| W3 I2C EEPROM On Board | 0x2200_0000 | 0x2200_FFFF | 64K |

| W3 Clock Controller | 0x2210_0000 | 0x2210_FFFF | 64K |

| W3 AD Controller | 0x2220_0000 | 0x2220_FFFF | 64K |

| Radio Controller | 0x2230_0000 | 0x2230_FFFF | 64K |

| Mailbox | 0x3000_0000 | 0x3000_FFFF | 64K |

| Mutex | 0x3100_0000 | 0x3100_FFFF | 64K |

| WLAN PHY TX | 0x4000_0000 | 0x4000_FFFF | 64K |

| WLAN PHY RX | 0x4100_0000 | 0x4100_FFFF | 64K |

| WLAN MAC HW | 0x4200_0000 | 0x4200_FFFF | 64K |

| WLAN AGC | 0x4300_0000 | 0x4300_FFFF | 64K |

| W3 User IO | 0x8000_0000 | 0x8000_0FFF | 4K |

| WLAN MAC Time HW | 0x8100_0000 | 0x8100_0FFF | 4K |

| BRAM (RX pkt buffer) | 0x9000_0000 | 0x9000_7FFF | 32K |

| BRAM (TX pkt buffer) | 0x9100_0000 | 0x9100_7FFF | 32K |

Last modified 8 years ago

Last modified on Dec 7, 2015, 3:02:59 PM

Attachments (1)

- 802_11_v1_4_interconnect_architecture.png (180.2 KB) - added by welsh 8 years ago.

Download all attachments as: .zip