WARP FPGA Board Multi-Gigabit Transceivers

The FPGA board provides 8 multi-gigabit transceiver connections for board-to-board links. These transceivers are each capable of 3.125Gb/sec full-duplex communication with another board. The MGTs are provided to enable very high-speed connections between multiple WARP FPGA boards for applications requiring the processing resources of multiple FPGAs.

For extensive documentation on using the MGTs, refer to Xilinx's Virtex-II Pro MGT Users Guide.

The MGT connections are arrayed along the top of the FPGA board, numbered 1-8 right-to-left.

| MGT | FPGA Instance | Tx +/- Pins | Rx +/- Pins |

| 1 | GT_X1Y1 | A35/A36 | A34/A33 |

| 2 | GT_X2Y1 | A31/A32 | A30/A29 |

| 3 | GT_X3Y1 | A27/A28 | A26/A25 |

| 4 | GT_X4Y1 | A23/A24 | A22/A21 |

| 5 | GT_X5Y1 | A18/A19 | A17/A16 |

| 6 | GT_X6Y1 | A14/A15 | A13/A12 |

| 7 | GT_X7Y1 | A10/A11 | A9/A8 |

| 8 | GT_X9Y1 | A6/A7 | A5/A4 |

MGT Clocking

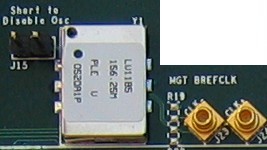

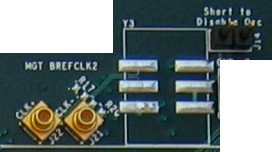

MGTs require reference clocks provided by very low jitter differential oscillators. The WARP FPGA board includes footprints for two such oscillators. One is mounted by default; the other is left unmounted for future customization.

The MGTs require clocks driven into specific pins on the FPGA, refered to as BREFCLK and BREFCLK2. The left oscillator (component Y1) drives BREFCLK; the right oscillator (component Y3) drives BREFCLK2. The pin mapping for these clock signals are:

| Clk Input | Schematic Name | FPGA Pin |

| BREFCLK+ | MGT_CLK0P | E20 |

| BREFCLK- | MGT_CLK0N | D20 |

| BREFCLK2+ | MGT_CLK1P | J20 |

| BREFCLK2- | MGT_CLK1N | K20 |

| BREFCLK Oscillator | BREFCLK2 Oscillator |

|

|

The oscillators can be disabled by mounting shunts on the adjascent 2-pin headers. When disabled, the reference clock can be driven to the FPGA through a pair of MMCX connectors. This allows multiple FPGA boards to share a common MGT reference clock, which enables an applicaiton to bypass the high-latency elastic buffers in the transceivers.

VTRX Configuration

The Rx termination voltage for the middle four of the FPGA board's MGTs can be configured for 1.8v or 2.5v. VTRX=2.5v is required for DC-coupled connections to other FPGA boards. VTRX=1.8v is used when connected to devices with AC-coupling, like some third-party FPGA boards.

The other four MGTs are always configured for VTRX=2.5v.

The configuraiton is handled by mounting a shunt across two pins on a three pin header for each MGT. The bottom pins are shorted for VTRX=2.5v; the top pins for VTRX=1.8.v

Connectors & Cables

All eight MGTs are wired to Infiniband-keyed HSSDC2 jacks. You must use an Infiniband-keyed 100Ω HSDDC2-HSDDC2 cable to connect two FPGA boards together. One such cable is made by Molex (Molex HSDDC2 Cables).